Detailed explanation of APB protocol and comparison with 3.0-4.0-5.0

tags: ARM Hardware architecture Network protocol

Detailed explanation of APB protocol and comparison with 3.0-4.0-5.0

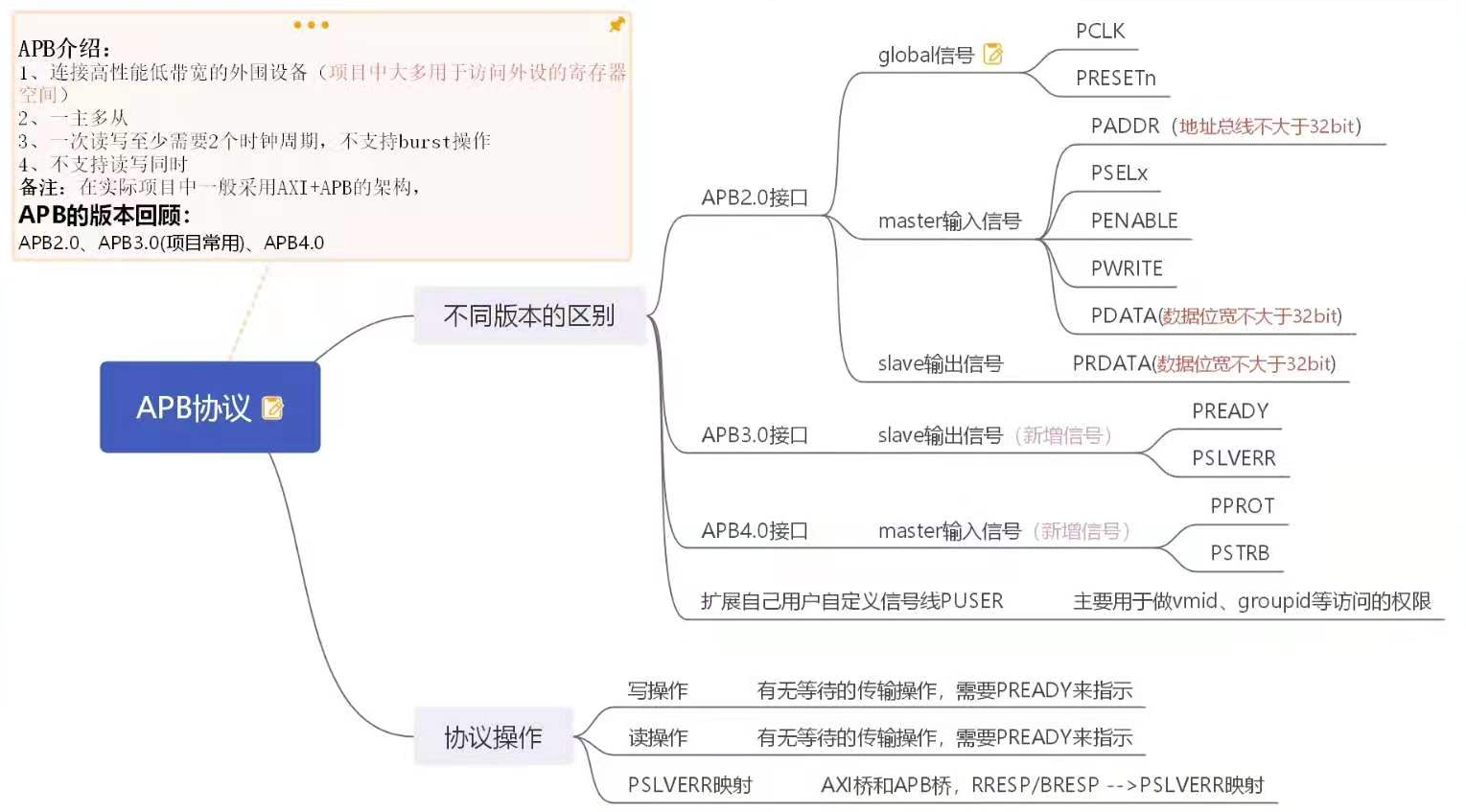

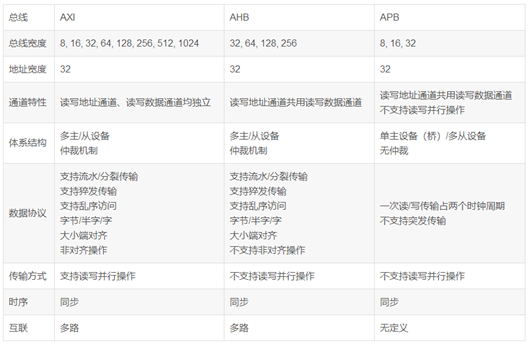

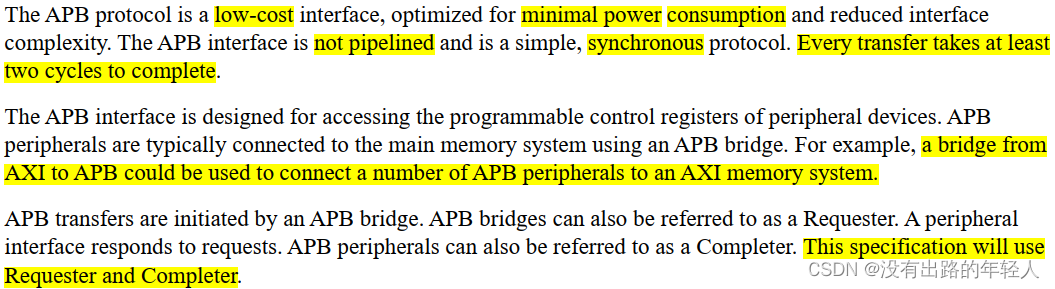

Among the AMBA buses, the APB bus is the most commonly used and the most basic bus. This article mainly summarizes the advantages and disadvantages of the APB bus, and compares the use of APB3.0 and 4.0, which are currently the most widely used. Introduction to 5.0

APB bus introduction

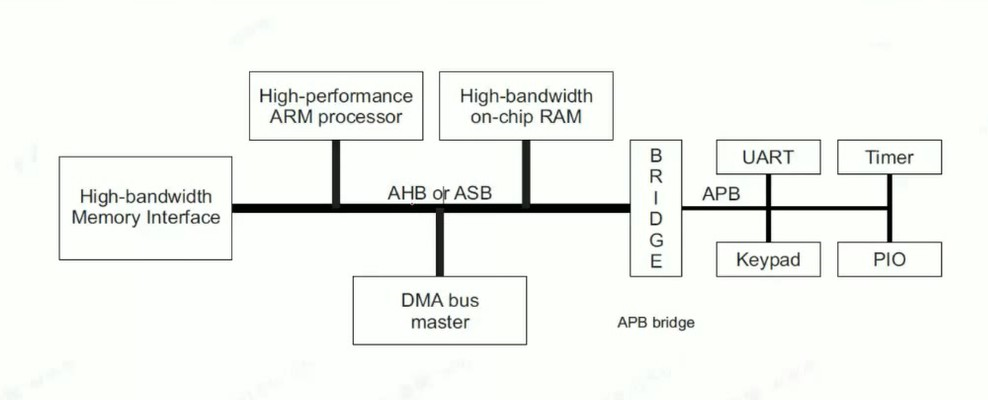

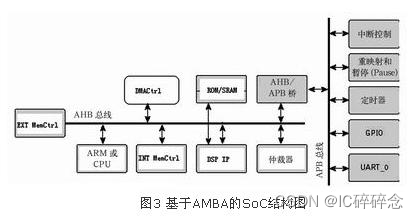

AMBA is an open protocol mainly used inside SoC and ASIC to connect various functional modules.

Most modules (including processors) hanging on the bus are only functional modules with a single attribute: master module or slave module. The master module is a module that issues read and write operations to the slave module, such as CPU, DSP, etc.; the slave module is a module that accepts commands and responds, such as on-chip RAM, AHB/APB bridge, etc. In addition, there are some modules that have both attributes at the same time. For example, direct memory access (DMA) is a slave module when being programmed, but it must be a master module when the system reads and transmits data. If there are multiple master modules on the bus, an arbiter is needed to decide how to control the access of various master modules to the bus. Although the arbitration specification is part of the AMBA bus specification, the specific algorithm used is determined by the RTL design engineer. The two most commonly used algorithms are the fixed priority algorithm and the round-robin algorithm. There can be up to 16 master modules and any number of slave modules on the AHB bus. If the number of master modules is greater than 16, an additional layer of structure is required (for details, please refer to the Multi-layer AHB specification introduced by ARM). **APB bridge is both the only master module on the APB bus and the slave module on the AHB system bus. ** Its main function is to latch the address, data and control signals from the AHB system bus, and provide secondary decoding to generate the selection signal of the APB peripheral device, thereby realizing the conversion of the AHB protocol to the APB protocol

Introduction to APB (Peripheral Bus)

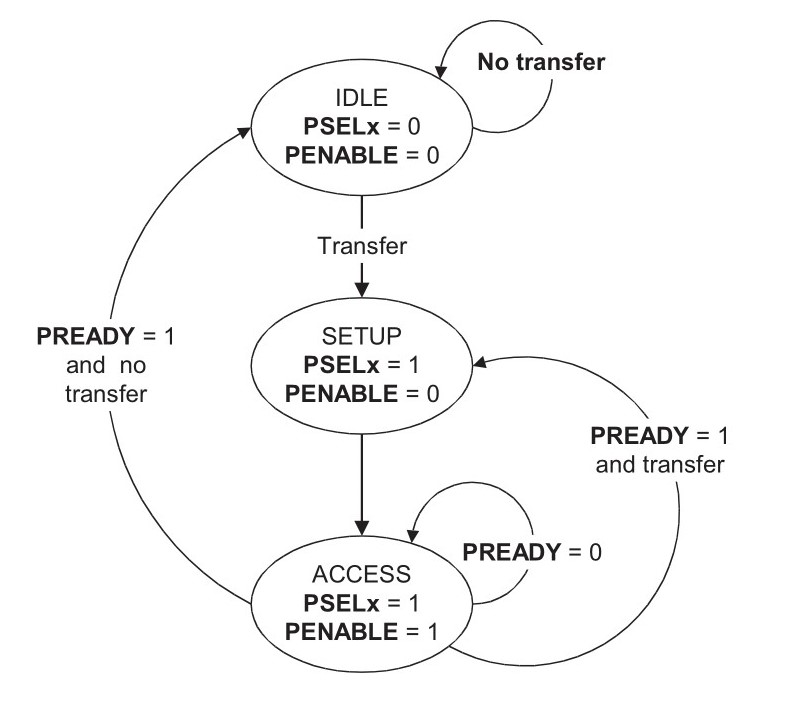

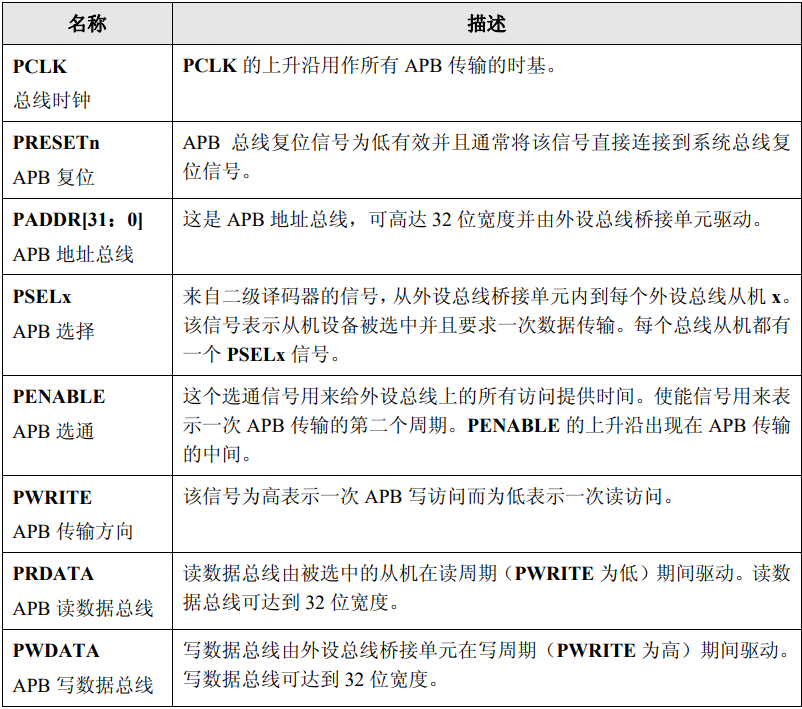

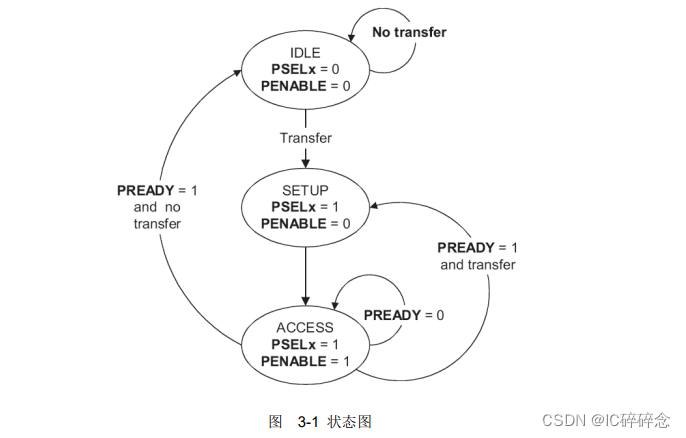

1) The system is initialized to the IDLE state. At this time, there is no transmission operation and no slave module is selected.

2) When there is a transmission to be carried out, PSELx=1, PENABLE=0, the system enters the SETUP state and will only stay in the SETUP state for one cycle. When the next rising edge of PCLK arrives, the system enters the ENABLE state.

3) When the system enters the ENABLE state, keep the PADDR, PSEL, and PWRITE in the SETUP state unchanged, and set PENABLE to 1. The transmission will only remain in the ENABLE state for one cycle and will be completed after passing through the SETUP and ENABLE states. After that, if there is no transmission to be carried out, it will enter the IDLE state and wait; if there is continuous transmission, it will enter the SETUP state (regardless of the prepare signal).

The above is the simplest and most basic data transmission on the APB bus (no waiting or error reporting)

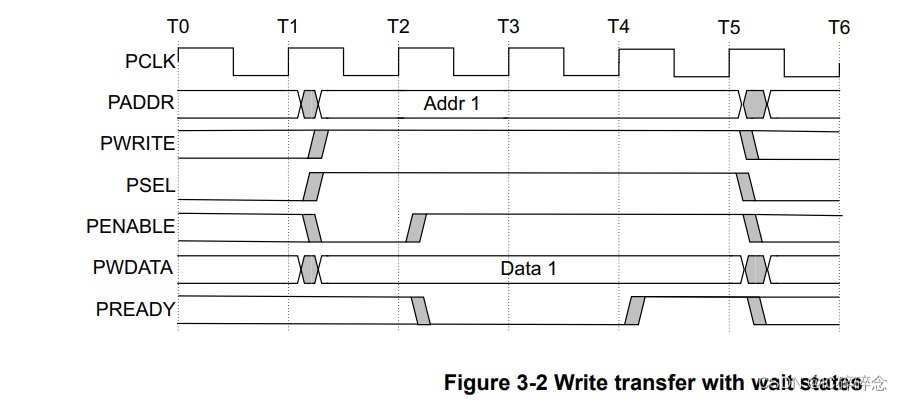

APB3.0 adds PREADY and PSLVER signals, PREADY is used to indicate the completion of APB transmission. APB_Slave directly tells the master through the PREADY signal that APB_Slave is now READY and can accept read and write operations. If it is not READY at this time, then the master will wait until it is Ready, so no software is needed. It’s time to poll the status register.

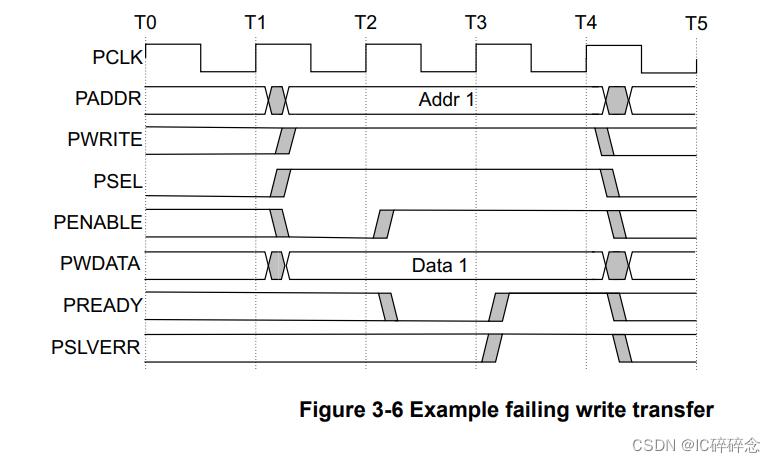

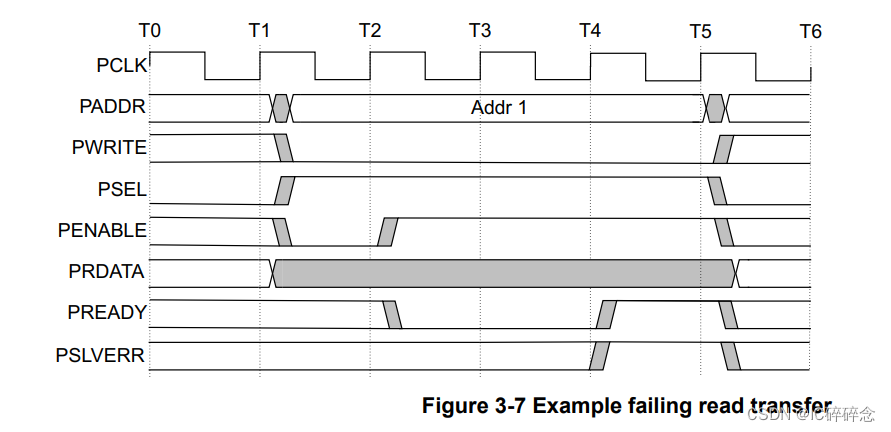

For PSLVERR, the slave error response function is added to the master. The pslverr signal is only valid in the last cycle of APB transmission, when the psel, penable, and prepare signals are all high. If the pslverr signal is set high, it means that the transmission failed, but it does not mean that the write to the register failed. The value of the register may still be updated. If data is read, it does not mean that rdate must be all 0.

After AMBA3.0 adds prepare: the jump of ACCESS status depends onoutput by slavePREADY signal status:

prepy and pslver are slave output signals.

1) If PREADY is 0, it means that the slave is not ready to receive data and will continue to be in the ACCESS state;

2) If PREADY is 1, it means that the slave has completed the data and can jump to other states. If there is continuous data transmission later, jump directly to SETUP; if there is no transmission, return directly to IDLE;

Application diagram about pslverr.

**From AXI to APB :**An APB error on PSLVERR is mapped back to RRESP for reads and BRESP for writes.

**From AHB to APB:**An APB error on PSLVERR is mapped back to HRESP for reads and writes.

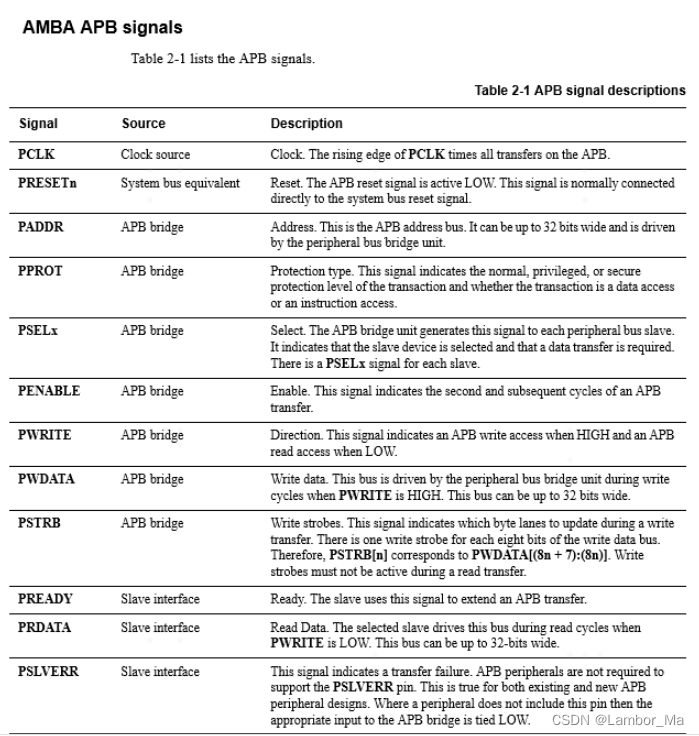

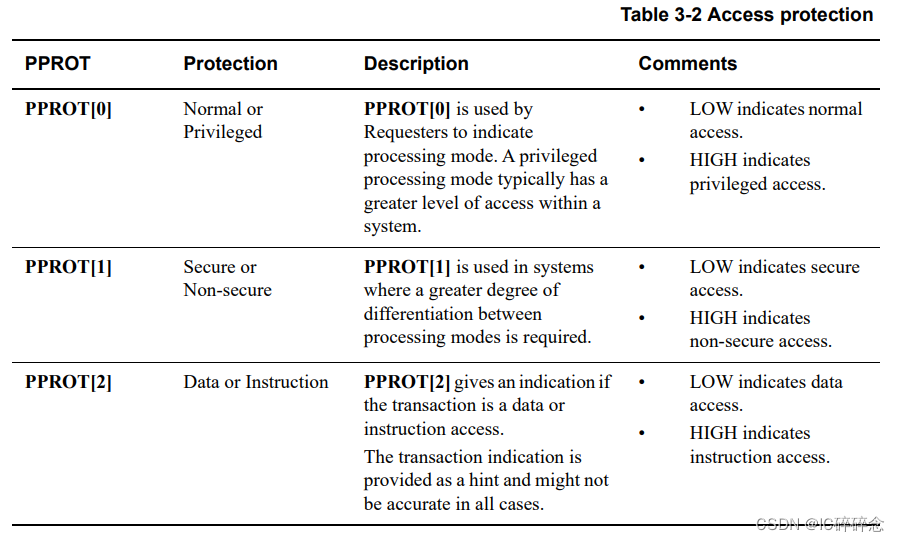

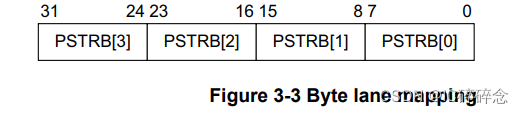

**APB4 adds PPROT (Transaction protection), PSTRB (Sparse data transfer). **Both signals are optional.

PPROTThe signal can mainly realize secure and non-secure data transmission, and can realize the control transmission of the system with different security attributes to ensure the security of the system.

PPROT[0]Represents the transmission of different priorities, which can realize special processing operations of salve on data of different priorities.

PPROT[1]Indicates data transmission of different security attributes and data processing of Secure and Non-secure data. Non-secure cannot change the area of the secure attribute.

PPROT[2]Used to indicate whether data or instructions are transmitted at this time.

PSTRBThe signal is used to realize the valid data bits of wdate[31:0] in one-write data transmission.

For read transfers, the Requester must drive all bits of PSTRB LOW

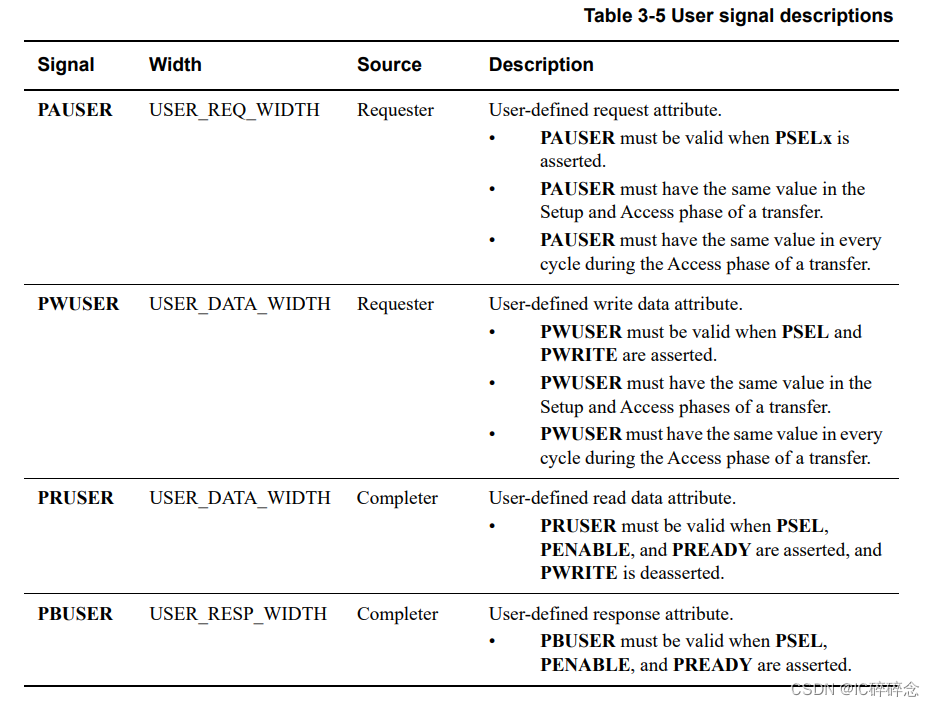

APB5 adds wake-up, user, pairty protection and check signals。

Wake-up is used to achieve low power consumption control. By controlling the clock to only turn on during transmission, it reduces dynamic power consumption. Used to indicate whether the component supports wake-up signals

user has increaseduser defined signal。

pairty protection and check signalsMainly aimed at the protection function in safety system design. To support secure transmission and security verification.

The solutions mainly include parity check or SECDED algorithm.

AMBA5 provides a parity check solution. The specific use can be decided by the user.

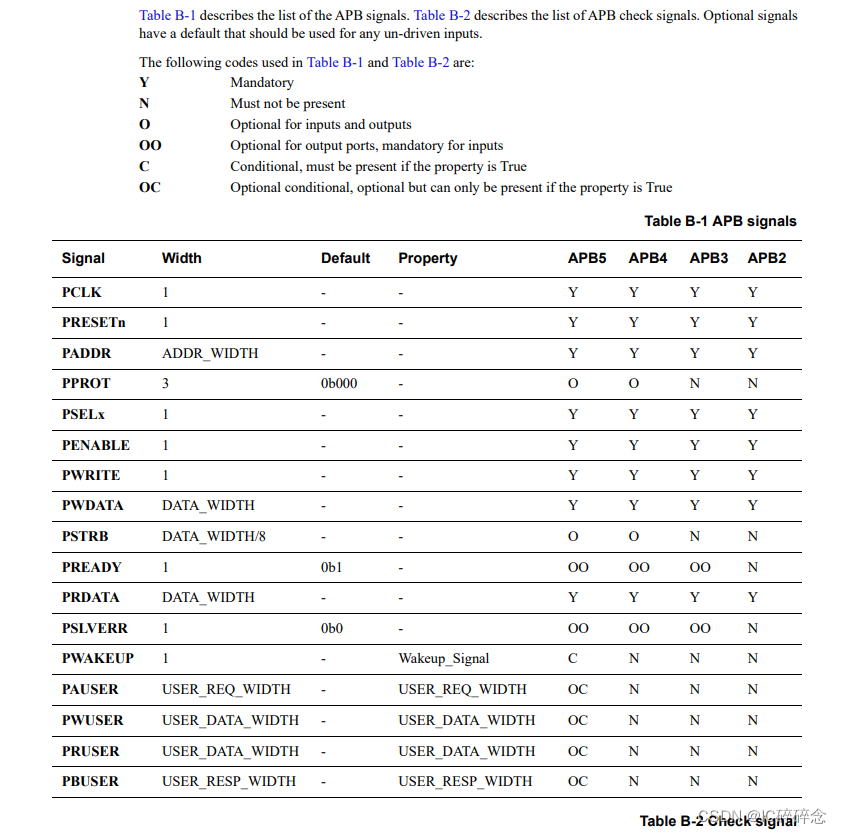

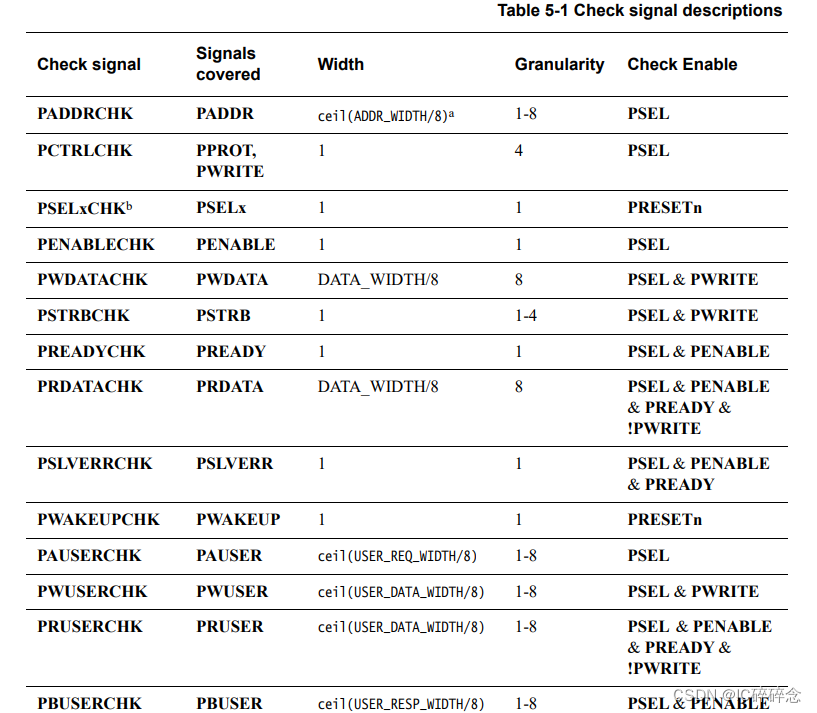

Each bit of the parity check signal covers up to 8 bits of data. The following table shows some APB signals and corresponding check signals.

Summary of APB bus features

The APB bus has only one master, and the others are slaves.

APB bus transfers are read and write operations to data targets and always require at least 2 bus cycles

Can work at high frequencies;

Simple agreement: No complicated timing; only four control signals. (PSEL, Pwriter, Penable, Pread)

synchronous bus: All transactions (read and write operations) on the bus depend on the rising edge of the clock;

One master, many slaves: Under normal circumstances, APB is hung under the AHB bus system, and transactions are converted between AHB bus systems through the AHB-APB Bridge. At this time, Bridgre is the master of APB, and other peripheral devices are slaves. ****

APB is mainly used for connections between low-bandwidth peripherals, such as UART, I2C, etc.,

IHI0024D_amba_apb_protocol_spec.pdf

Intelligent Recommendation

Some features of apb protocol

APB is mainly used to connect high-performance and low-bandwidth peripherals. In the APB bus system, there is only one master, and the others are slaves. Features: ① Can work under high frequency; ② S...

AMBA bus APB protocol

APB introduction The bus is used in the SOC to complete interconnection between each device, and in the bus standard, the ABMA bus developed by ARM is most common, this article is used to introduce an...

APB protocol learning notes

APB introduction APB (Advance Peripheral BUS) is part of the AMBA bus. It is a low-cost interface that is designed with minimum power consumption and reduced port complexity. The APB interface is used...

APB protocol learning

APB(Advanced Peripheral Bus) 1. Overview and characteristics of APB The APB is mainly used for connections between peripheral peripherals, such as UART, 1284, etc., its bus architecture is not like AH...

APB protocol and APB_SLAVE design

1. APB protocol original: translate: The APB protocol is alow costThe interface is optimized,Reduce power consumption and interface complexityEssence APB interface isSimple,Synchronize,Water -free wat...

More Recommendation

APB protocol learning (reprinted)

APBThe agreement isARMIn the companyAMBAA kind of agreement. The earliestAPBThe agreement is now calledAPB2, and laterAPB3andAPB4。APBThe protocol is backward compatible, and over time, according to ac...

Introduction to AMBA-APB protocol

Catalog of series articles Article Directory Catalog of series articles Preface 1. APB 2. APB signals 3. Write transfers no wait states wait states 4. Read transfers no wait states wait states 5. Erro...

AMBA Protocol—APB Protocol 2.0

1.APB 2 signal list Here we need to distinguish the difference between Master and Slave. Master is a switchboard, and Slave is a slave. There can be n slaves under a switchboard. All data transmission...

EventBus 3.0 uses detailed explanation

Original address: 01 Foreword When we develop a project, it is often necessary to communicate between the components and components of the application and the background thread, such as request data i...

Detailed Explanation of Servlet 3.0 (4)

ServletContext performance enhancements In addition to these new features, ServletContext object features in the new version has also been enhanced. Now, the object supports dynamic deployment of Serv...