Vivado HLS (High-level Synthesis) note 1: HLS basic flow

Preface

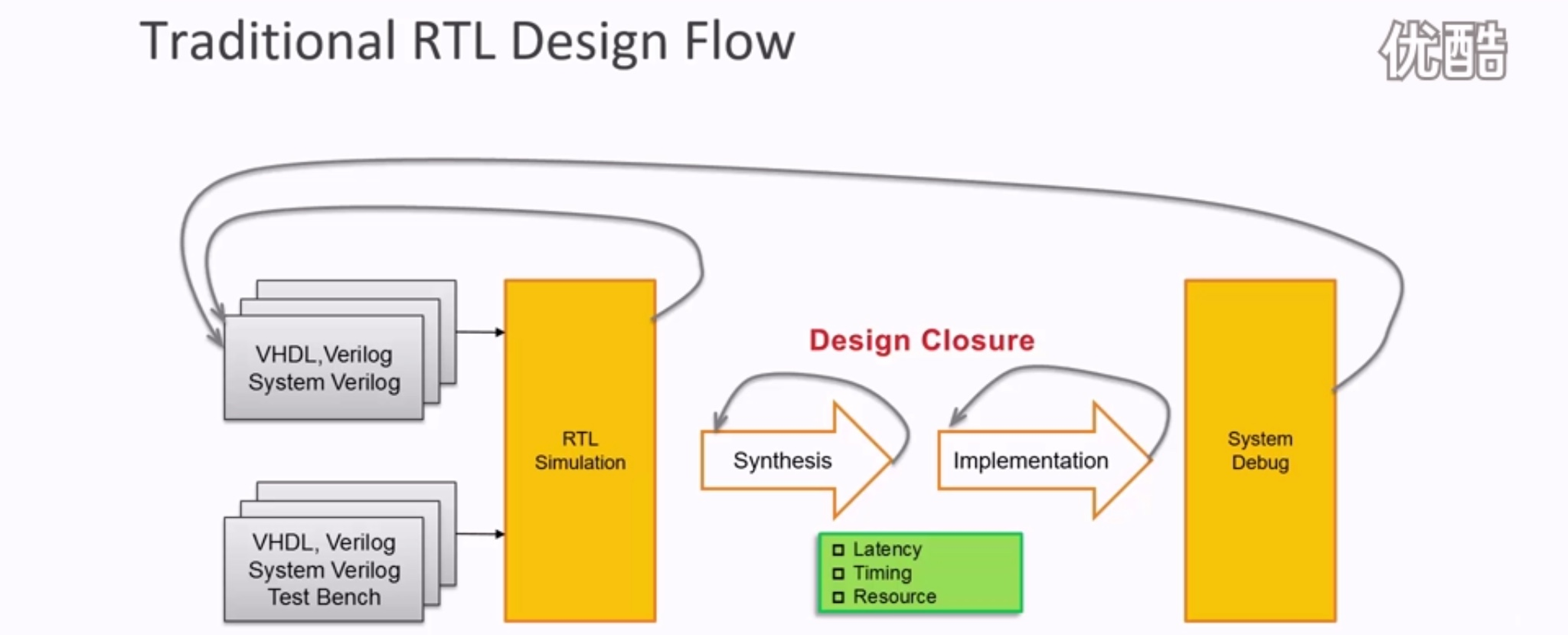

The laboratory project needs to configure the network parameters that ran out of the server section to the FPGA. One method is to directly use verilog or vhdl to write a forward propagation model of the network, and the other is to use C/C++ to describe The forward propagation model of the network is then converted into a hardware description language-verilog or vhdl using Vivado's HLS. The first method has high resource utilization, but it needs to consider timing and parallelism (two important factors in hardware language design), which is more difficult; the second method is relatively efficient and a little easier; as a novice, in line with For the idea of running through the process, I chose the second method as the first attempt. I learned it through the video class of teacher Gao Yajun, and attached the link:

Let’s talk about the difference between CPU, GPU, DSP, and FPGA first:

For a software engineer, what should be mastered:

- The function of each unit in FPGA;

- The specific algorithm operation and the corresponding relationship between each unit;

- The utilization of resources in the algorithm model;

- Optimization method of algorithm model;

To sum it up, just one sentence"How can we make the HDL code converted into C/C++ run efficiently?”

1. The working principle of Vivado HLS

1. History of ESL(Electronic System Level)

CAD-CAE-EDA

- Computer Aided Design

- Computer Aided Engineering

- Electronic Design Automation

At this stage of EDA, the most typical feature is the emergence of hardware description languages-VHDL and Verilog;

Up to now, the concept of ESL (Electronic System Level Design Method) has emerged. Its essence is to say that at this stage of ESL we hope to use a higher degree of abstraction to describe system behavior, so there are two notable aspects at this stage feature:

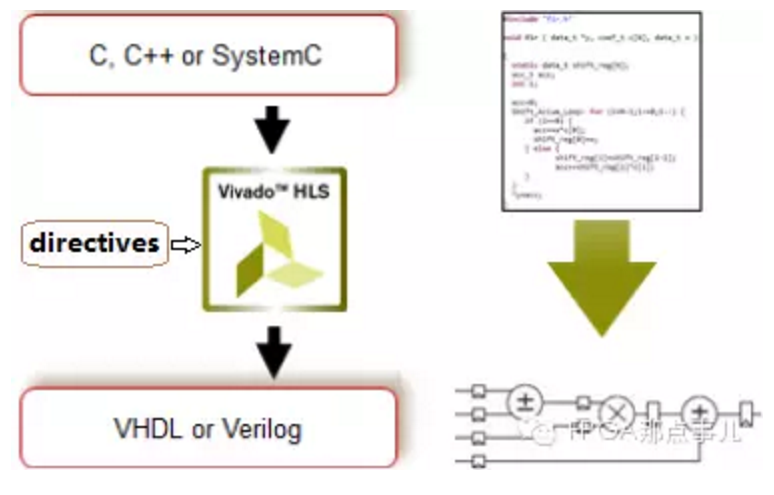

- Use high-level language (such as C or C++), XILINX has Vivado HLS tool;

- Use model-based design tool-System Generator;

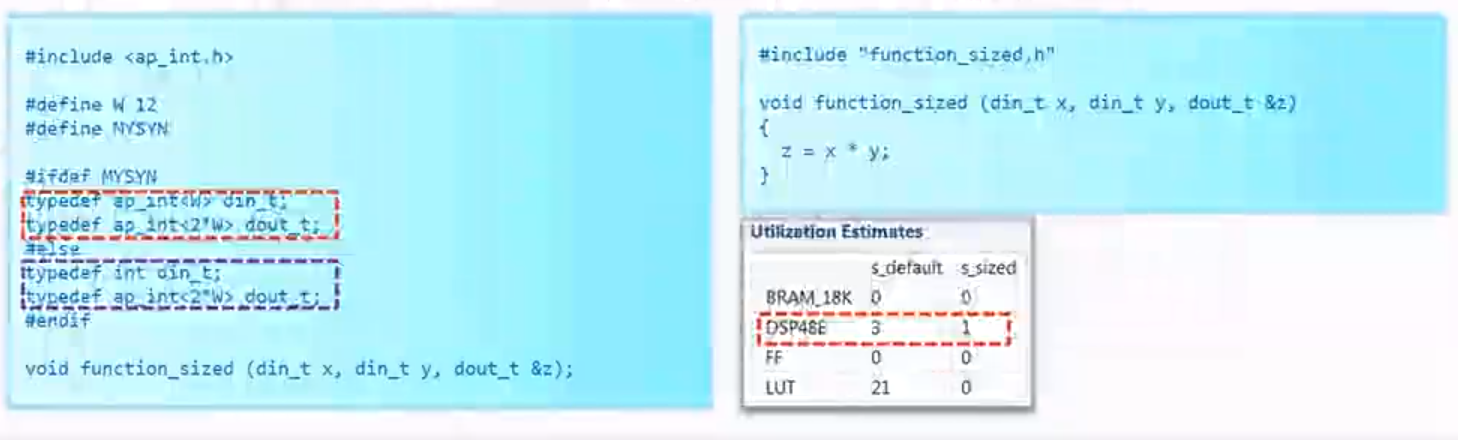

2. High-level Synthesis Benefits

- For hardware engineers, improving project efficiency does not need to consider parallelism and timing issues, and directly consider optimization at the algorithm level;

- For software engineers, system performance can be improved. Algorithms that originally required CPU, GPU or DSP can now be implemented through FPGA, which improves throughput on the one hand and power consumption on the other;

- Develop and verify algorithms at the C/C++ level;

- Use optimization tools to efficiently guide the conversion process;

After the algorithm description is completed, a corresponding text is needed to test our algorithm,

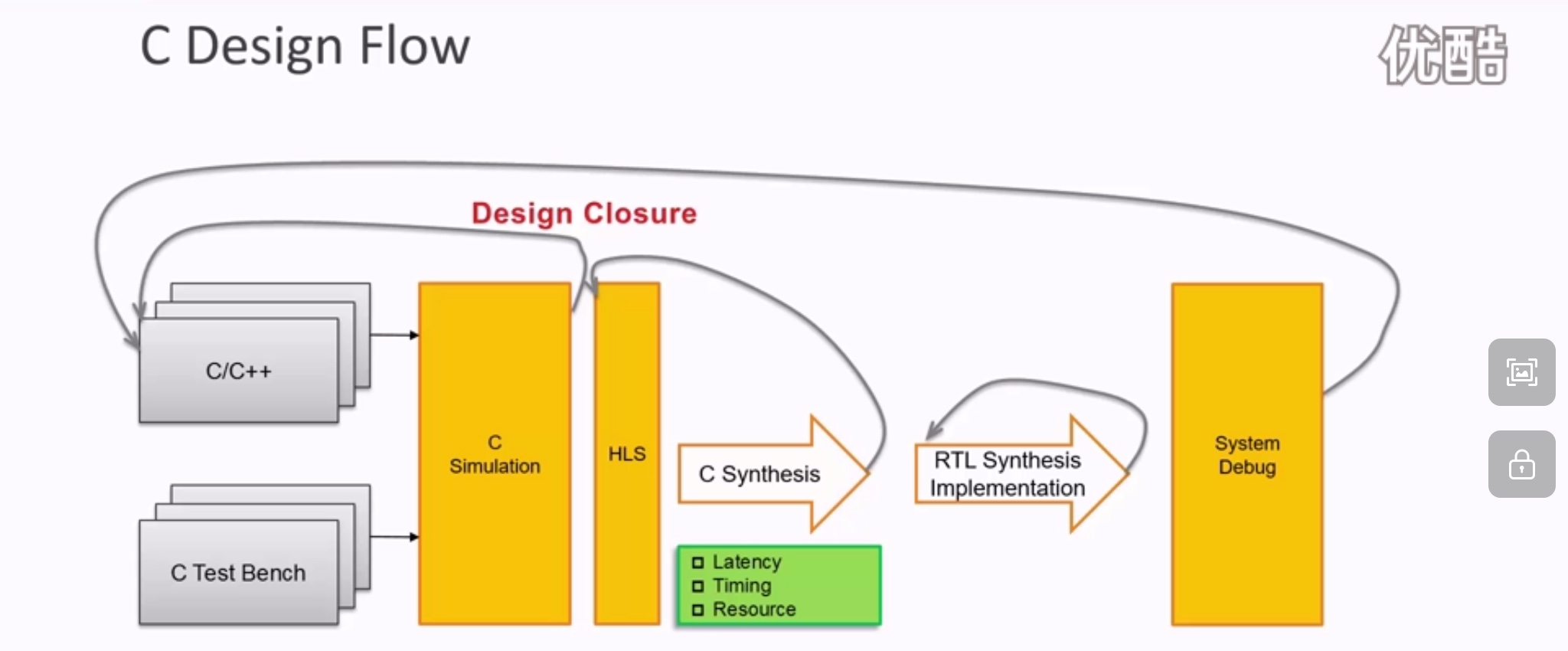

3. The integrated process of Vivado HLS

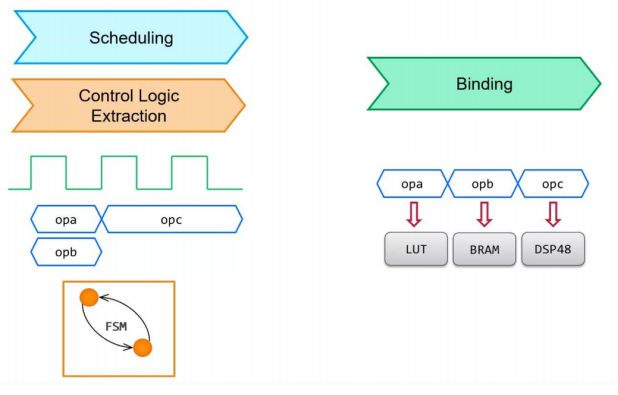

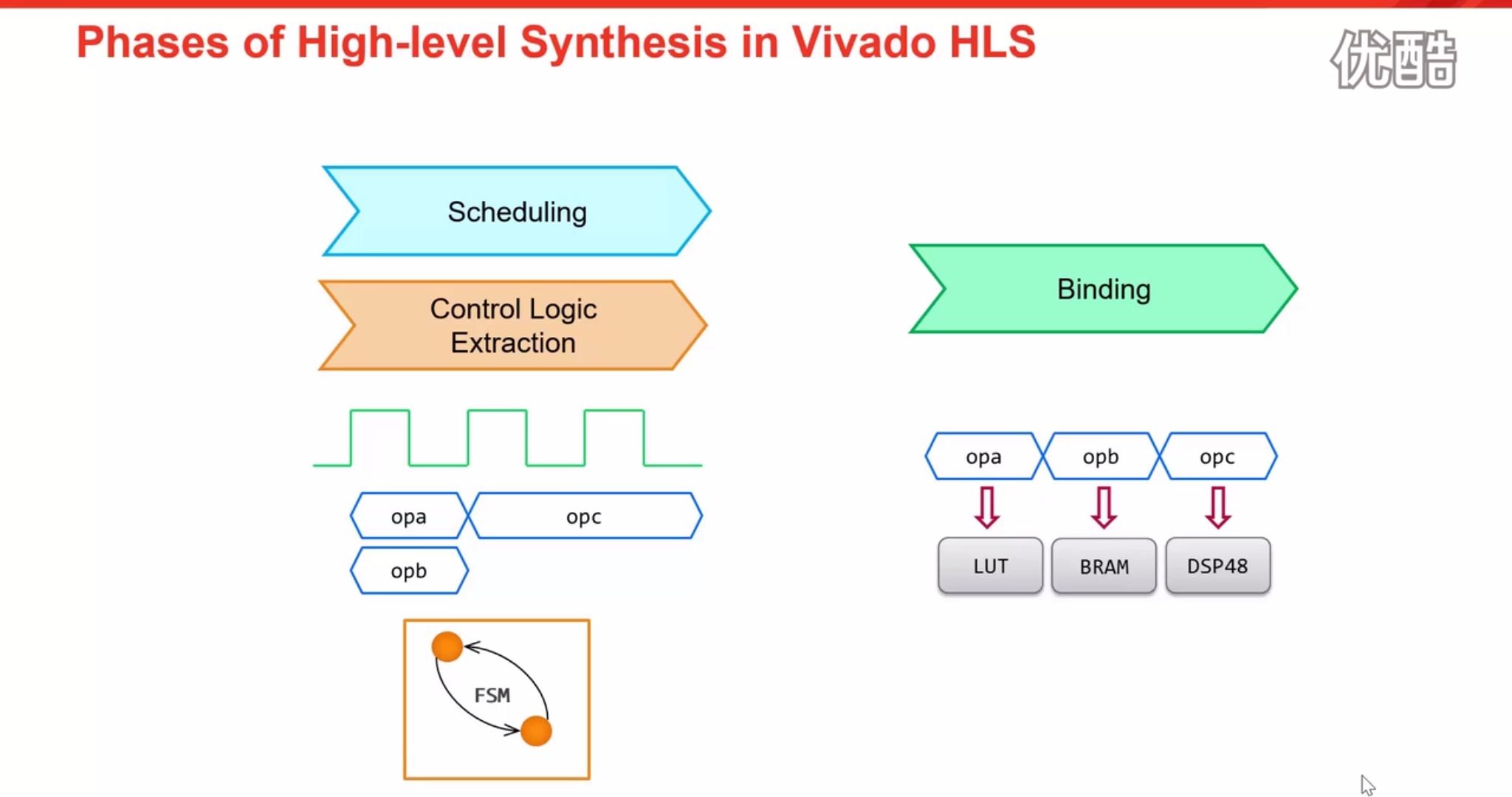

- Scheduling: Determine what operation should be done in each clock cycle. At the same time, this operation may take several clock cycles to complete, and whether it can be executed in parallel;

- Control Logic Extraction: The extraction of control logic usually generates a state machine, which can be seen in the HDL code;

- Binding: Determine what resources each operation needs to be implemented, and complete such a process from operation to resource mapping;

Let's look at some examples of these processes:

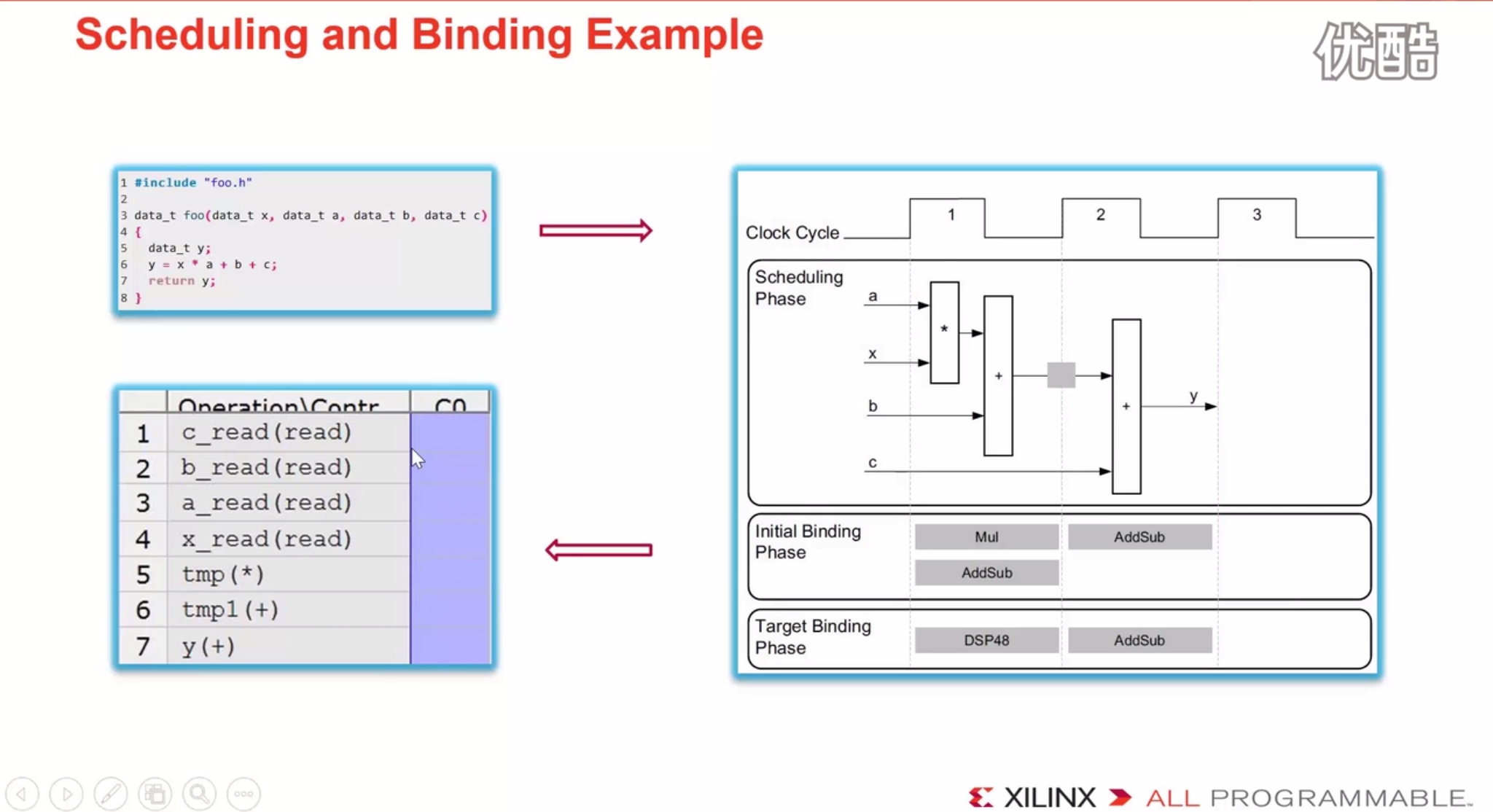

The example of Scheduling and Binding Example is as follows, the following example is relatively simple, so there is only one state C0;

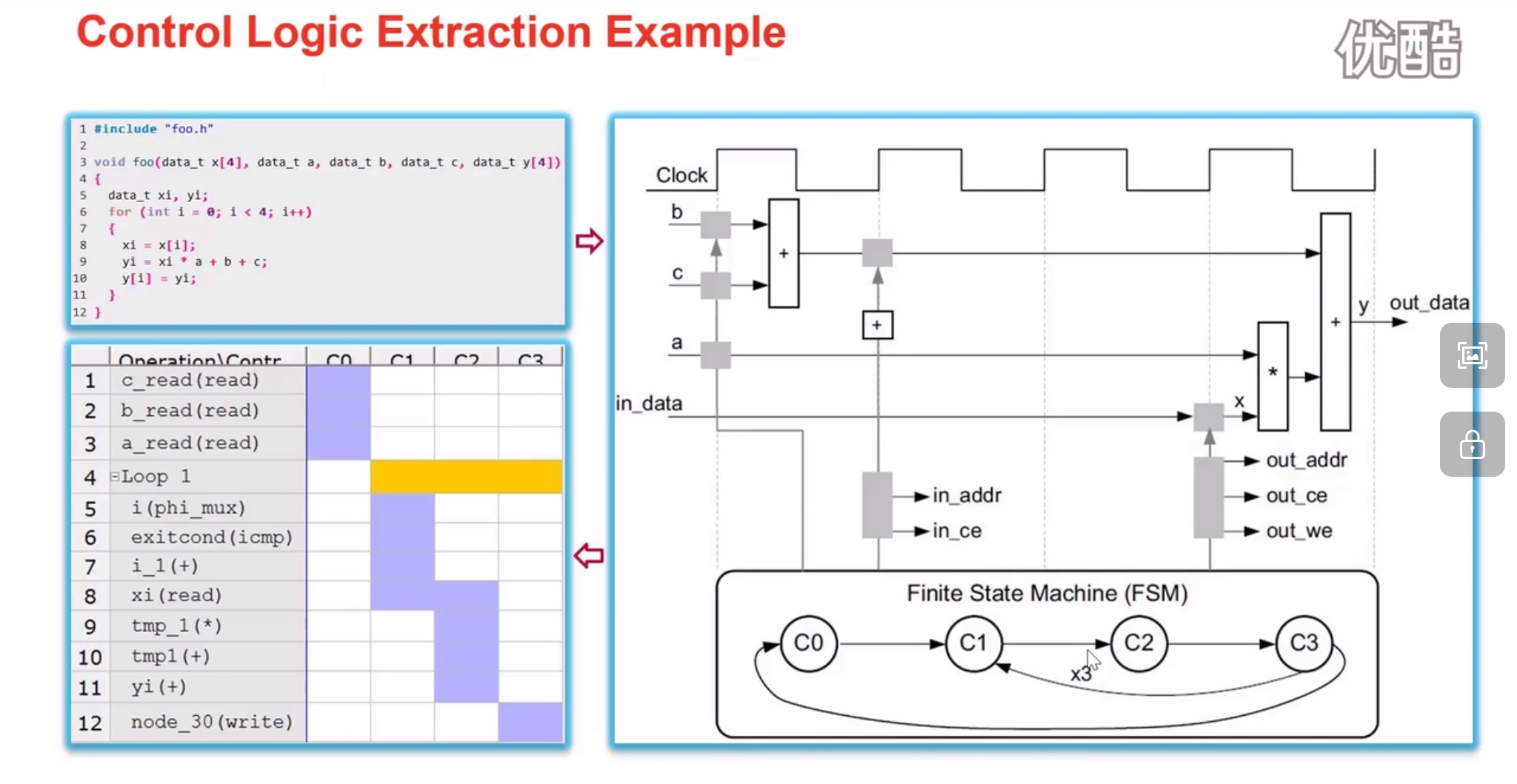

Extend to the logic extraction example, there are four states, in the C0 state execute b+c, the C1 state generates x and the address of the array, the C2 state executes the corresponding multiplication operation, and the C3 state The result is written into the corresponding bit of the y array, and the loop is repeated several times until it reaches the loop boundary and exits the loop. It should be noted that the generated control state (bottom left) and the state machine (bottom right) are not in a one-to-one correspondence, but they are very close.

4. Vivado HLS design flow

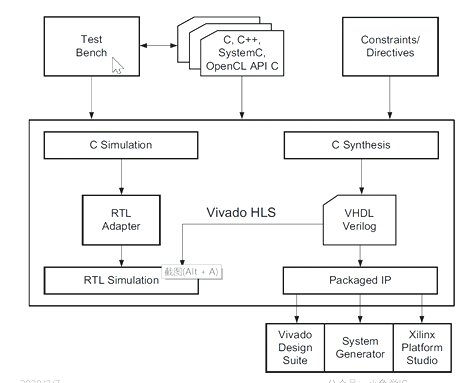

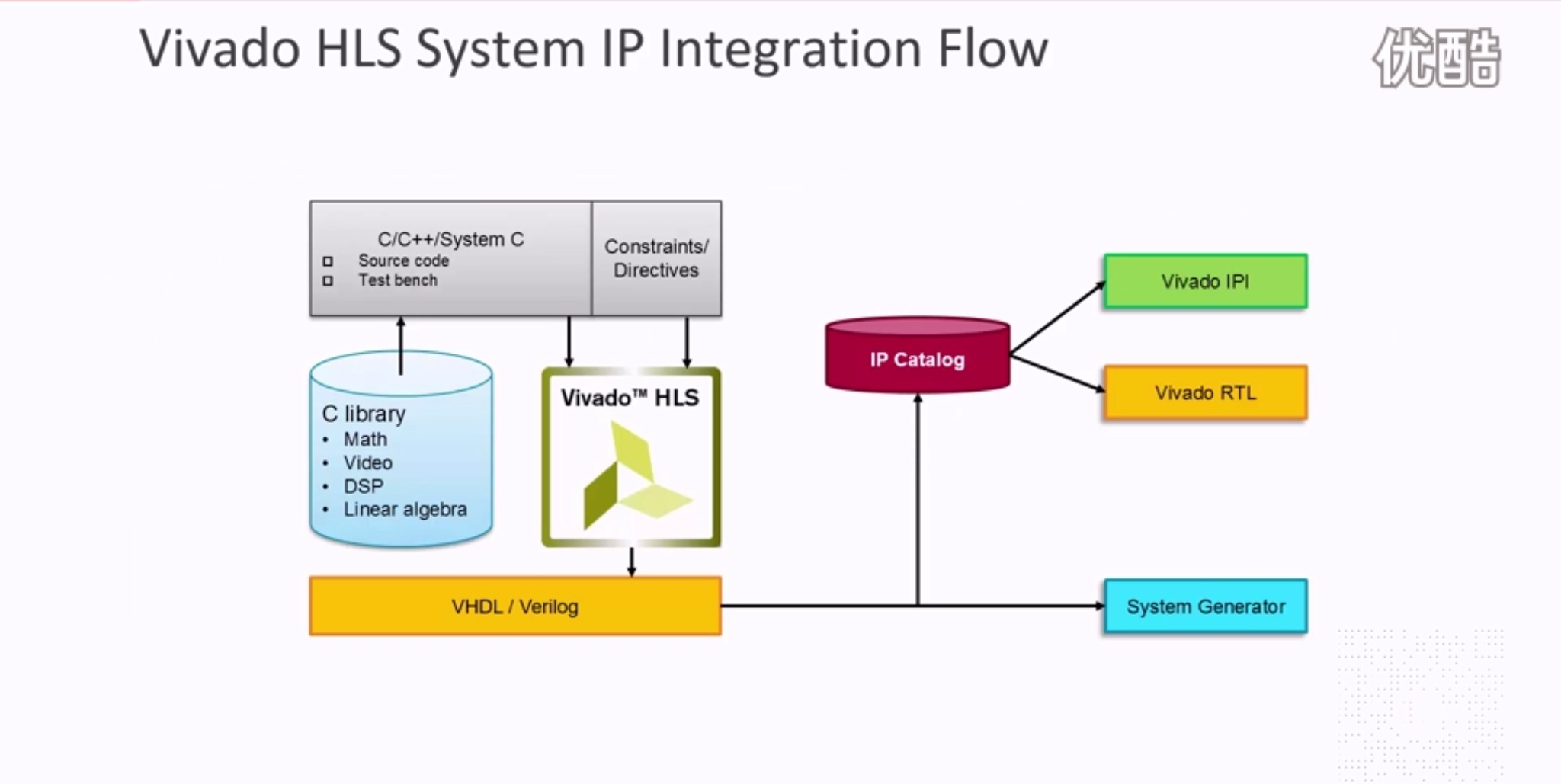

- The design input of Vivado HLS includes Test bench, C/C++ and Directives. The corresponding design output includes IP (in Vivado's IP Catalog), DCP (netlist file after RTL code synthesis), SysGen (results after HLS can be imported) Used in SysGen).

- The test bench has two functions: one is to verify the correctness of the C/C++ code; the other is to generate a test bench for RTL-level verification during the co-simulation phase with RTL;

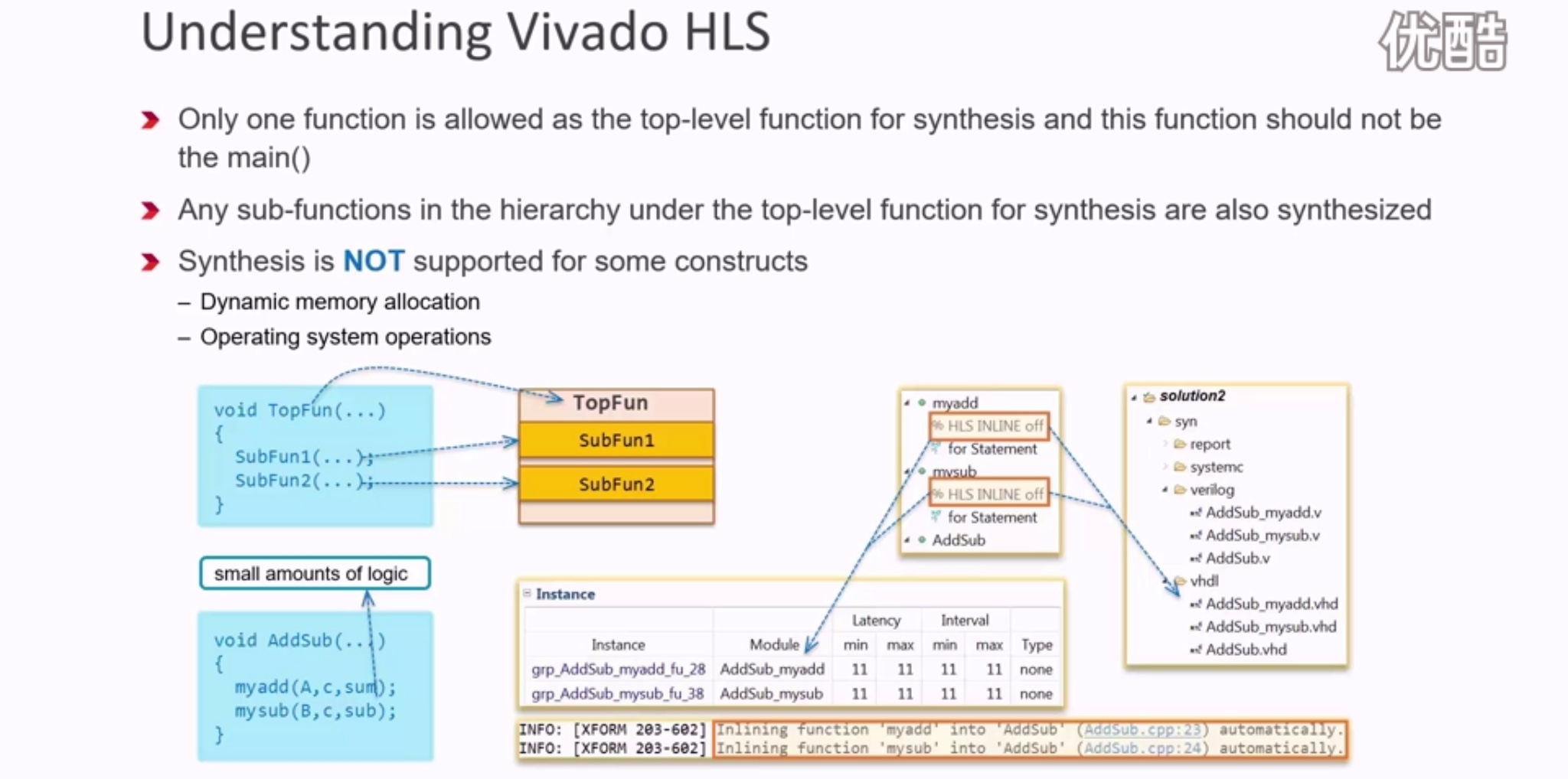

- For a project, only one top-level function can be used for synthesis, and the sub-functions below this function can also be synthesized. Normally, the structure of the RTL code after C/C++ synthesis is the same as the structure described by the original C function (except When the logic required by the sub-function is very small and the algorithm function is very simple, the synthesis stage will not have this structure alone, and it will be completely consistent when the HLS INLINE off is turned off).

- Not all C/C++ language style codes can be synthesized. There are two points to note: One isDynamic memory allocation, the second is the operating system level;

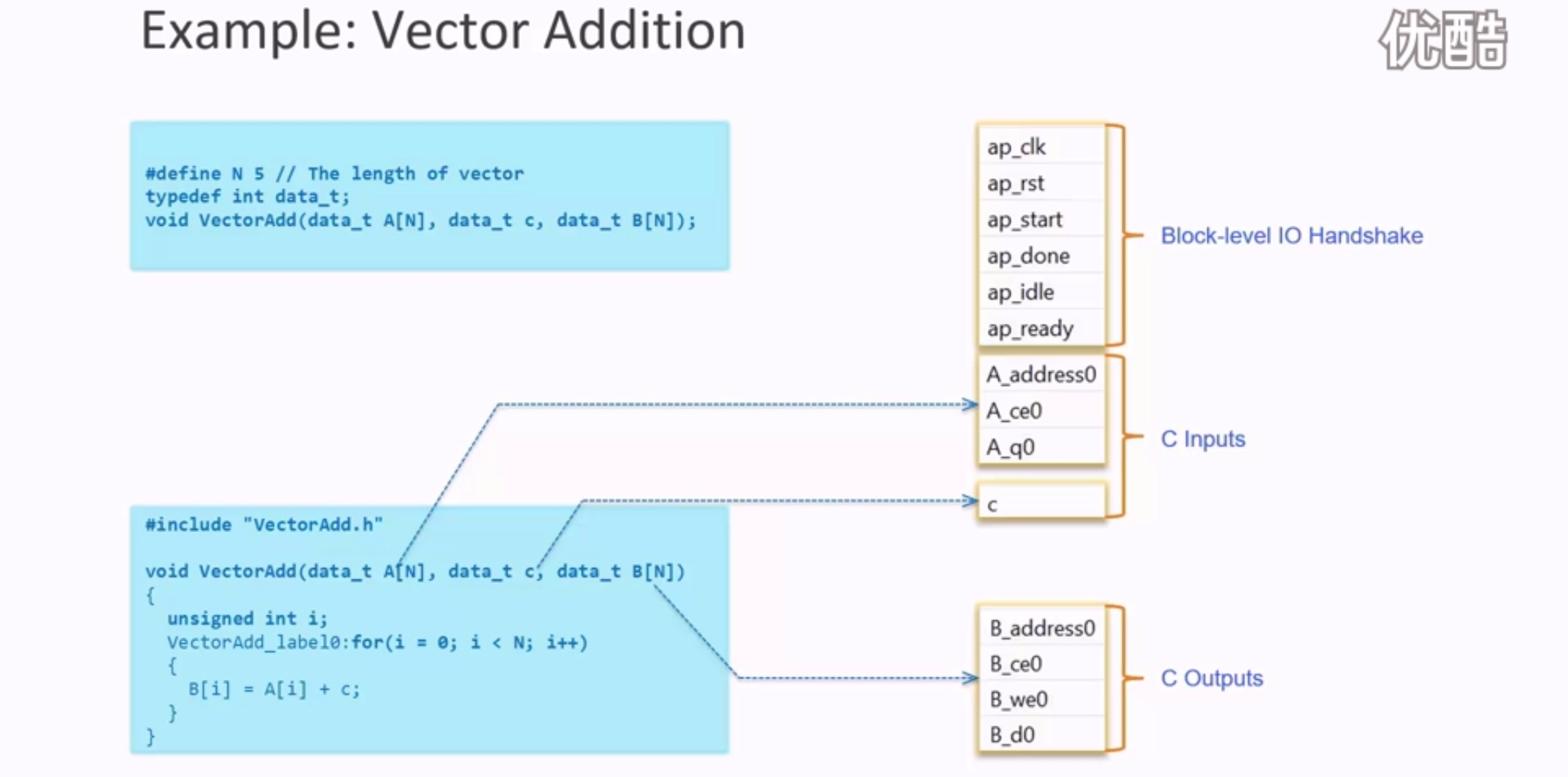

- A C/C++ code finally maps to RTL code, there are three types of interfaces, including Block-level IO Handshake (handshake signal), C Inputs, C Outputs;

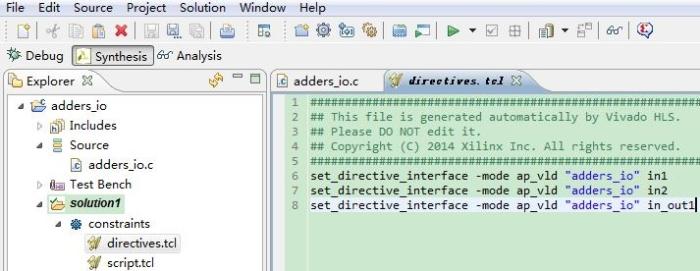

Two ways of Directives:

-

Store each directive separately as a Tcl command in directives.tcl format, with "#" as the mark;

The advantage is: each solution has independent directives. If the solution needs to be re-synthesized, then only the directives under this solution will play a role; the disadvantage is: if the C source code If the file needs to be given to a third party, then the directives.tcl needs to be included. For a code that needs to obtain the same comprehensive result, then the same directives.tcl is essential. -

Embed each directive into the C/C++ source code and appear in pragma format, with "%" as the mark;

The advantage of is: if the C source code file needs to be given to a third party, there is no need to deliver the directives.tcl separately, and the same comprehensive result is required for a code, and no additional directives are needed. .tcl; The disadvantage is: if a solution needs to be re-synthesized, then all directives must be executed.

A few tips:

- Create a separate label for the for loop in the C/C++ code, which will make it very convenient when creating directives;

- It is best to store the directives separately, do not put them together with the source code;

- The return result value of the main() function in Test bench is of type int, the return value of simulation is 0, and it is 1 if it is not passed

- Under normal circumstances, the level of RTL code is consistent with the original C/C++ code level;

Intelligent Recommendation

Vivado HLS interface synthesis

Common types of interfaces in Vivado HLS are: 1. ap_none The default type, which does not apply to any I/O conversion protocol, is used to represent a read-only input signal that corresponds to the wi...

Windows vivado high level synthesis (HLS) to configure custom text editor and solve cases include path vscode

Windows vivado high level synthesis (HLS) to configure a custom text editor cases vscode Recently started using hls, vivado hls own editor experience is very bad, so would like to replace vscode, but ...

TCL command interface (scripting language) (High Level Synthesis) (FPGA) Vivado HLS in

Foreword: This example comes from the official Xilinx HLS Manual - (UG871), shows how to create a TCL script-based command Vivado HLS project already exists and how to use TCL Interface (existing proj...

Vivado HLS Learn 1 Vivado HLS use

What is hls Vivado HLS——oneOne is to use advanced language to describe system behavior, that is, C/C ++ is used to achieve system modeling.Software engineers can use this to improve system...

Optimization of VIVADO HLS function level

Optimization of VIVADO HLS function level references Project Overview type of data Implement inline operations on functions Allocation operation of function Function dataflow operation to sum up refer...

More Recommendation

Vivado HLS development steps (advanced synthesis) (FPGA)

For Vivado Hls, the input includes Tesbench, C/C++ source code and Directives, and the corresponding output is IP Catalog, DSP and SysGen. In particular, a project can only have one top-level funct...

Explanation of common time terms in high-level synthesis (HLS)

Explanation of common time terms in high-level synthesis (HLS) references Project Overview HLS working principle High-level integration (HLS) indicators to sum up references [1], Xiaoyu FPGA (WeChat p...

HLS (High-Level Synthesis) detailed explanation-loop body parallel optimization

HLS advanced synthesis can achieve hardware acceleration of software code, mainly because it optimizes the parallelism of the loop body (for, while) in the code, and uses pipelining, expansion, mergin...

Vivado HLS 4: Basic Concept

Vivado HLS 4: Basic Concept Thanks to FPGA's public account, providing a lot of entry knowledge! This article references themselves: Basic concept of HLS: 1, HLS supports C, C ++ and Systemc as...

Vivado HLS 3: Basic Concept

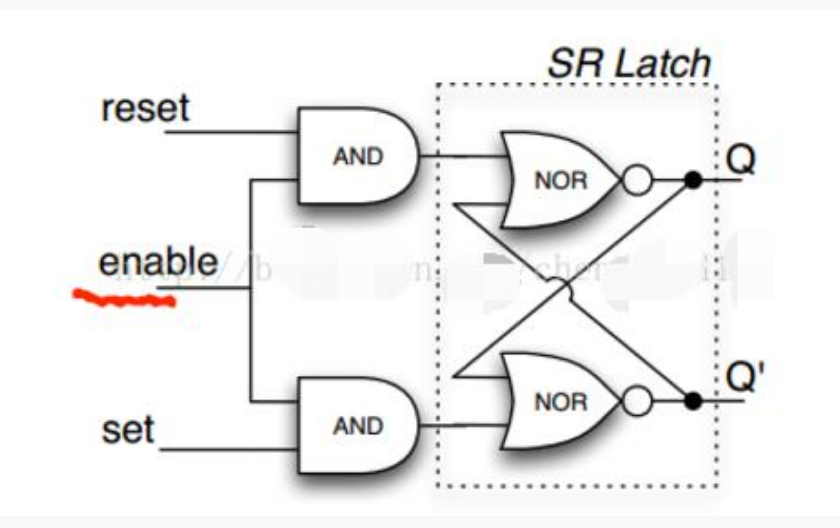

Vivado HLS 3: Basic Concept reference: Directory: 1. Concept of LUT, LATCH, FF in FPGA 2, LUT, LATCH, FF 's interrelationship 3, Verilog statement corresponds to the correspondence between LUT, LATCH,...