Verilog-based classic digital circuit design (17) sequence detector

tags: Classic digital circuit design based on Verilog verilog fsm

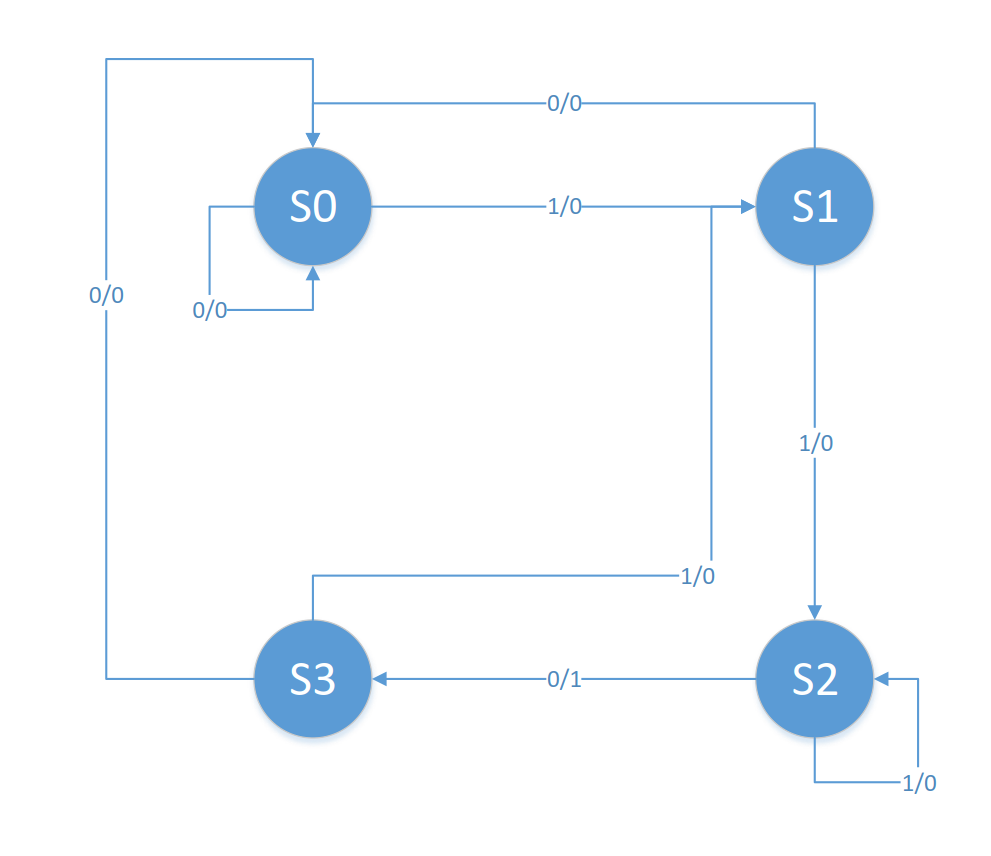

The finite state machine was introduced earlier. Next, we use FSM to design a 101 sequence detector.

The following is the Verilog code implementation of the 101 sequence detector:

module FSM(

input clk,

input rst_n,

input x, // input sequence

output reg z // test result

);

// FSM mainly includes current state CS, second state NS, and output logic OL;

parameter S0=2'b00,S1=2'b01,S2=2'b11,S3=2'b10; //Status coding, adopts Gray coding method, S0 is IDLE

reg [1:0] c_state,n_state;

/*------------------Conversion between the second state and the present state---------------*/

always @(posedge clk or negedge rst_n) begin

if(rst_n)

c_state <= S0;

else

c_state <= n_state;

end

/*-------Combination logic that converts the current state to the next state under input ------*/

always @(c_state or x) begin

case(c_state)

S0:begin

if(x)

n_state<=S1;

else

n_state<=S0;

end

S1:begin

if(x)

n_state<=S1;

else

n_state<=S2;

end

S2:begin

if(x)

n_state<=S3;

else

n_state<=S0;

end

S3:begin

if(x)

n_state<=S1;

else

n_state<=S2;

end

default:n_state<=S0;

endcase

end

/*--------------Combination logic from current state to output---------------*/

always @(c_state) begin

case(c_state) // This moment from S3 to S2;

S3: z=1'b1;

default:z=1'b0;

endcase

end

endmodule

Intelligent Recommendation

Classic digital circuit design based on Verilog (16) finite state machine

state machine! ! ! Very important! Very important! Very important! Say the important thing three times! Finite State Machine (Finite State Machine): Maybe you haven’t done a relatively large FPG...

Classic digital circuit design based on Verilog (15) parity checker

Parity Check is a method of verifying the correctness of code transmission. It is checked according to whether the number of "1"s in a set of binary codes being transmitted is odd or even; u...

Classic digital circuit design based on Verilog (7) JK flip-flop and T flip-flop

Uh...Why don't you just upload the code directly, these two triggers are rarely used, you probably understand them. The following is the Verilog code implementation of JK trigger: The RTL circuit d...

Classic digital circuit design based on Verilog (6) D flip-flop and Latch latch

D flip-flop is a necessary basic unit of sequential logic circuit. To learn D flip-flop is a prerequisite for learning sequential logic circuit. Its importance is no less than that of adder. The two t...

Verilog-based classic digital circuit design (11) string-in and string-out device

Serial-in/serial-out device, that is, a simplified version of FIFO without read-full-write-full flag, read-enable write-enable flag, etc. Although this is not very practical in the circuit, it is very...

More Recommendation

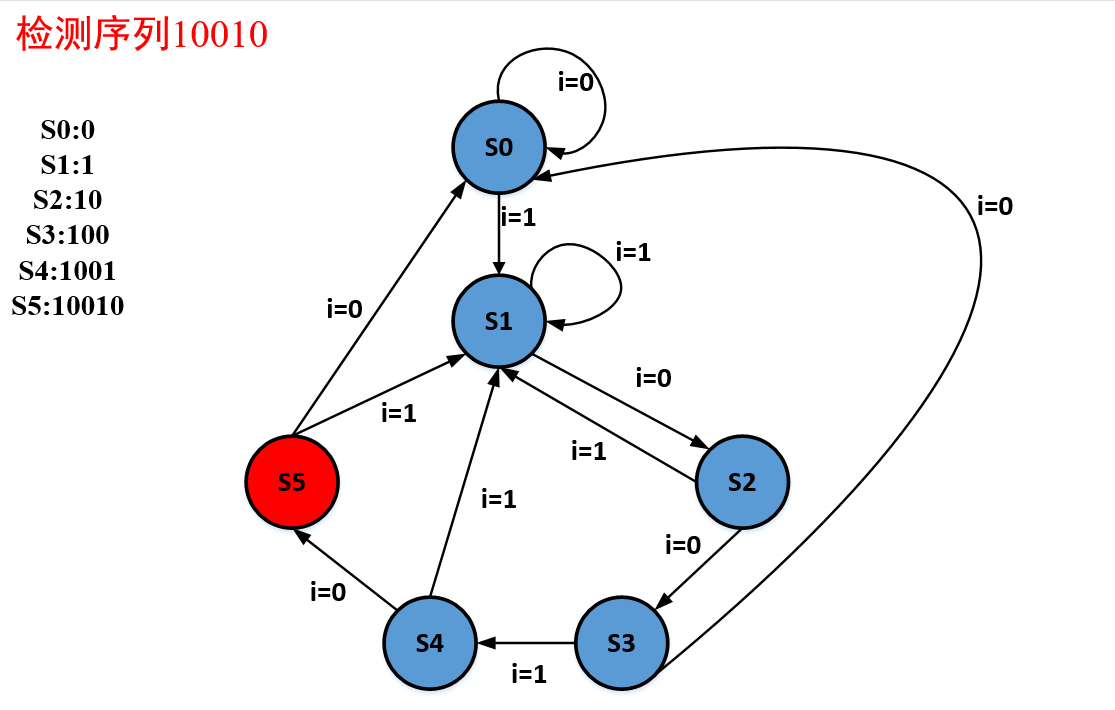

Sequence detector based on System Verilog

This article realizes a 10010 sequence detector through System Verilog Status machine design The state machine is a very important concept in digital circuit design. Many complex controls can be compl...

1101 sequence detector, based on Verilog HDL

Detect 1101, if yes, output 1, otherwise output 0; The source code is the standard Moore three -stage state machine. source code: Test code: Use {$ Random} % b to generate random numbers Simulation re...

Design of verilog-"10101" state machine sequence detector

First, draw a state transition diagram Code: Test code: Simulation results: The more you are, the more you have to work hard....

011 sequence detector design (predicted 2019 Shandong University graduate entrance examination digital circuit 906)

(15 points) The design method of the 011 sequence detector is similar to the design method of the 110 sequence detector/101 sequence detector, except that the original stat...

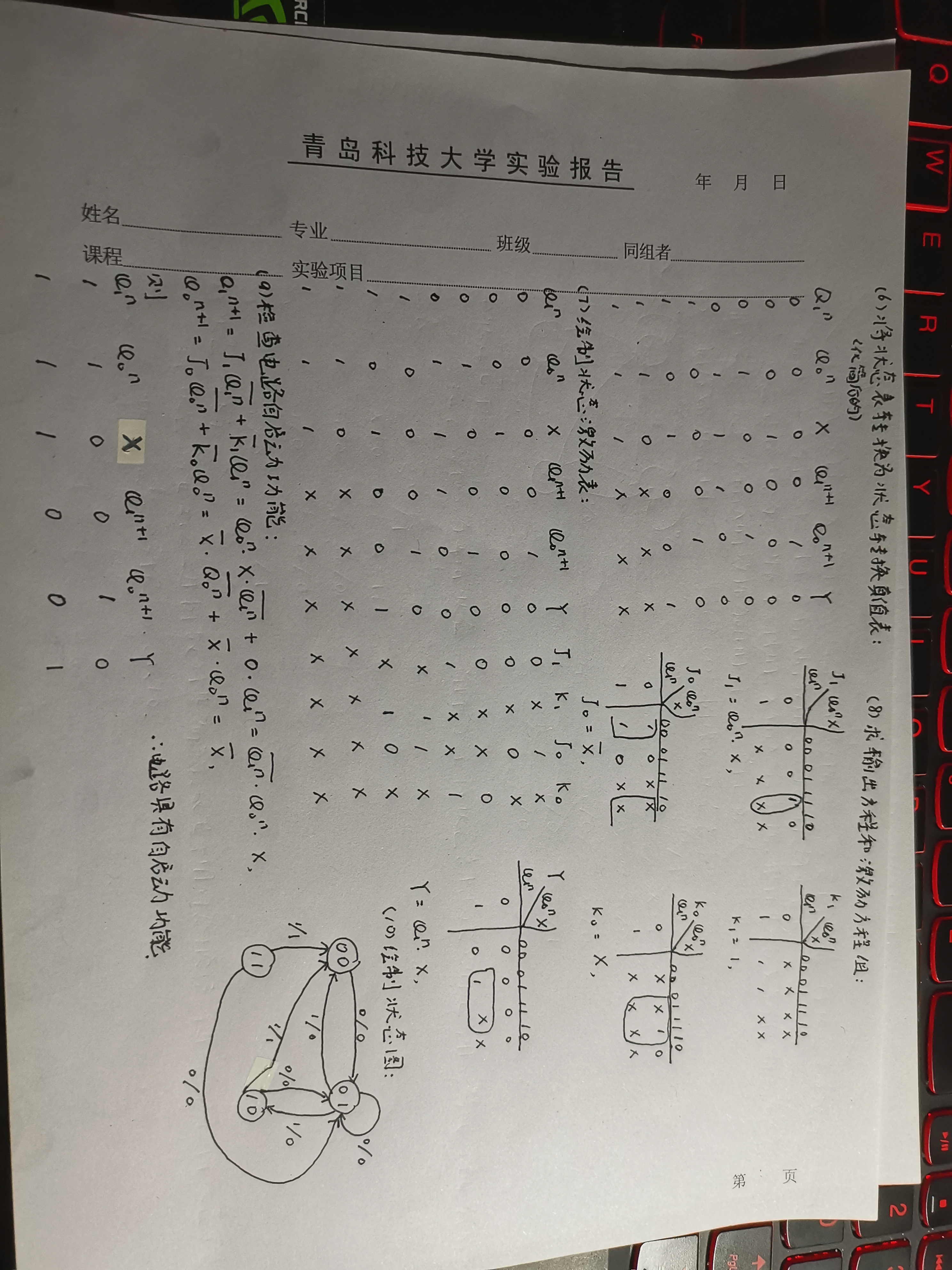

110 sequence detector design (2018 Shandong University graduate entrance examination digital circuit 906 finale question)

110 sequence detector design: (1) Logical abstraction: Suppose the input data is X; To input 3 continuous data, at least 4 states are required, set the state variable to、、、; The output variable is Y, ...