PCIe LTR Basic Knowledge

LTR:Latency Tolerance Reporting

LTR is an optional feature specified in the PCIe protocol, which can be used to improve the power management efficiency of the system.

By LTR, the PCIe device can inform the system how much they can tolerate, as long as the system responds to the request asked by the PCIe device within this time. The system's power management policy can be optimized according to the information provided by the LTR. When the device is required, the system quickly responds to the request proposed by the device; when the device is not required, the system can delay a response to the device request, as long as it does not exceed the time specified in the device LTR message. For example, if the system receives the request from the device while the system is low, then the request will respond to this request, avoiding frequently waking up from the low power state.

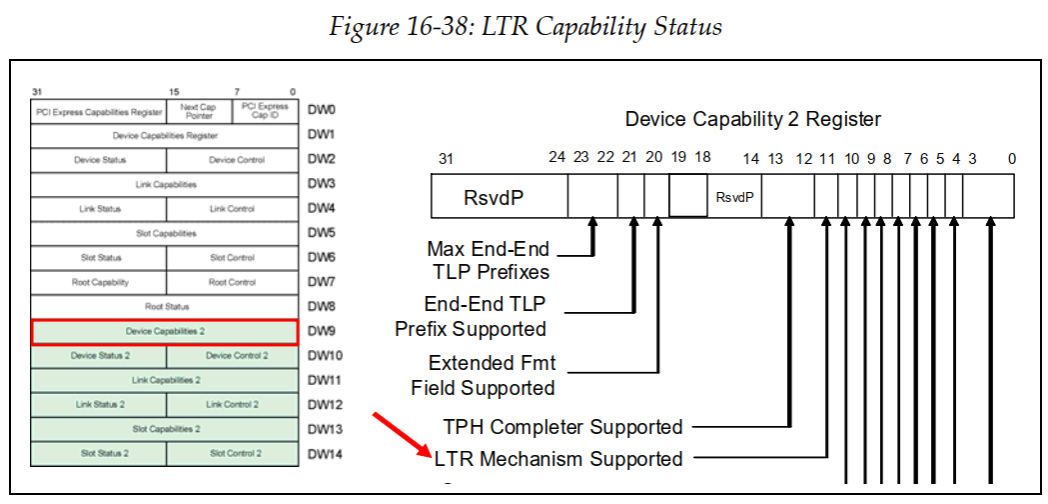

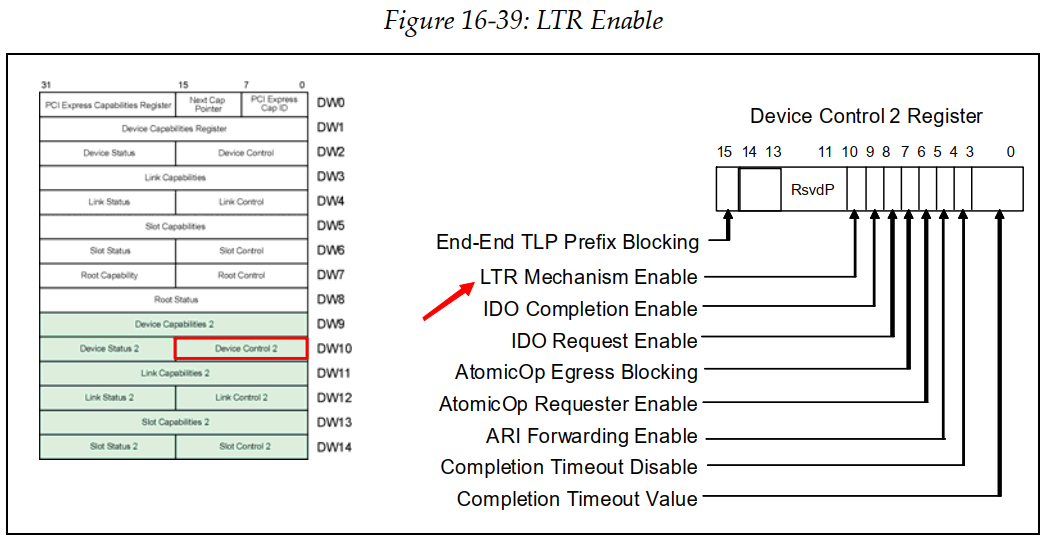

LTR register

The Device Capability 2 register in the PCIe configuration space indicates whether the device supports LTR, as shown below:

The Device Control 2 register in the PCIE configuration space indicates whether the device enables LTR, as shown in the following figure:

The PCIe protocol stipulates that when the LTR of the PCIe device should be enabled, the equipment close to the root complex should be enabled. The endpoint LTR can only be enabled when the EndPoint connected root port and the intermediate Switch support and enable LTR.

In the same PCIe bus system, endpoints that support LTR and EndPoints that do not support LTR are intended.

If root port or switch receives LTR messages from EndPoint without supporting LTR or does not enable LTR, you should take it in accordance with UNSUPPORTED REQUEST.

It is recommended that endpoint sent the LTR message immediately after being enabled. At the same time, it is highly recommended that the LTR message sent within 500 US is not more than 2 unless the protocol requires this.

LTR information is to be sent to root complex. The downstream port of Root Complex may pick up a lot of Endpoint, and each endpoint will send LTR information. Root Complex selects the minimum value as the actual usage standard in all LTR information received.

2. LTR Message (LTR Message)

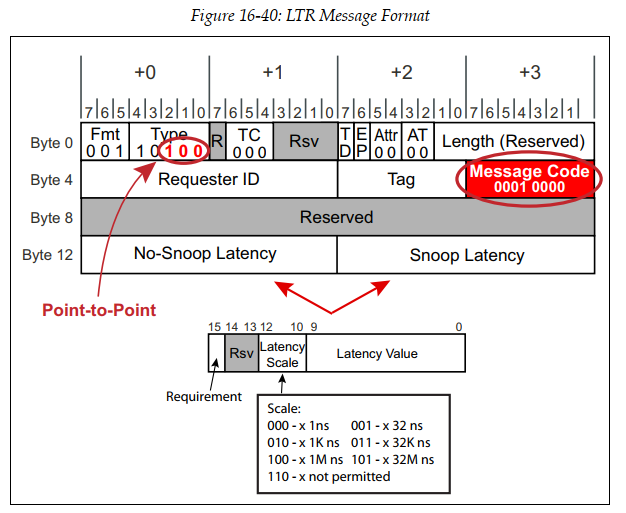

The LTR message format is shown below:

The LTR message includes two latency values: no-snoop latency and snoop latency. The same format is the same:

- Latency Value and Scale: These two parameters can be used in conjunction with Latency to 1 nanosecond ~ 34 seconds. If you set these two values to 0, it means that any delay affects the device, so the system needs to respond to the request in the first time. For different request types, the significance of Latency is as follows:

- For a read request, Latency means the start of the End ID from the read request TLP until the period of the first Completion TLP is received.

- For the write request, Latency means starting from the ENDPOINT write request TLP to start until the endpoint can issue this period of the next write request. The write request will receive the impact of the Flow Control. For example, endpoint issues a write request, its upstream port (UPSTREAM) Credits (ROOT port or Switch) of CREDITS causes EndPoint to continue to send the next write request. Only endpoint received the opposite DLLP to inform it that after sufficient Credits, EndPoint will continue to send a new write request. In this scenario, Latency is sent from the END request from the first write request until this time is received from the STP identity that releases the DLLP of Credits.

- Requirement: Do you need latency value. Can be set to 0 or 1. For example, if the PCIe device does not issue a NO-SNOOP request or the NO-SNOOP request does not have a Latency demand, then the Requirement bit of the NO-Snoop Latency area in the LTR message can be set to 0. If the PCIe device A issues a LTR message, the device B accepts this message does not enable the LTR message or the device is lower than the power consumption, the device A needs to send a LTR message again, and put the message The Requirement bit is set to 0.

The images in this article are from MINDSHARE, INC Classic book "PCI Express Technology".

More PCIe knowledge, click on the link.

Intelligent Recommendation

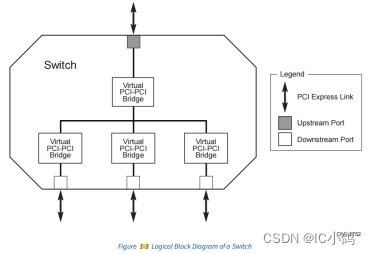

PCIE knowledge point-008: Structure of PCIE switch

1. Basic structure of Switch The switch structure diagram is shown in Figure 1-3. The switch contains an upstream port and several downstream ports. The upstream port and downstream port are connected...

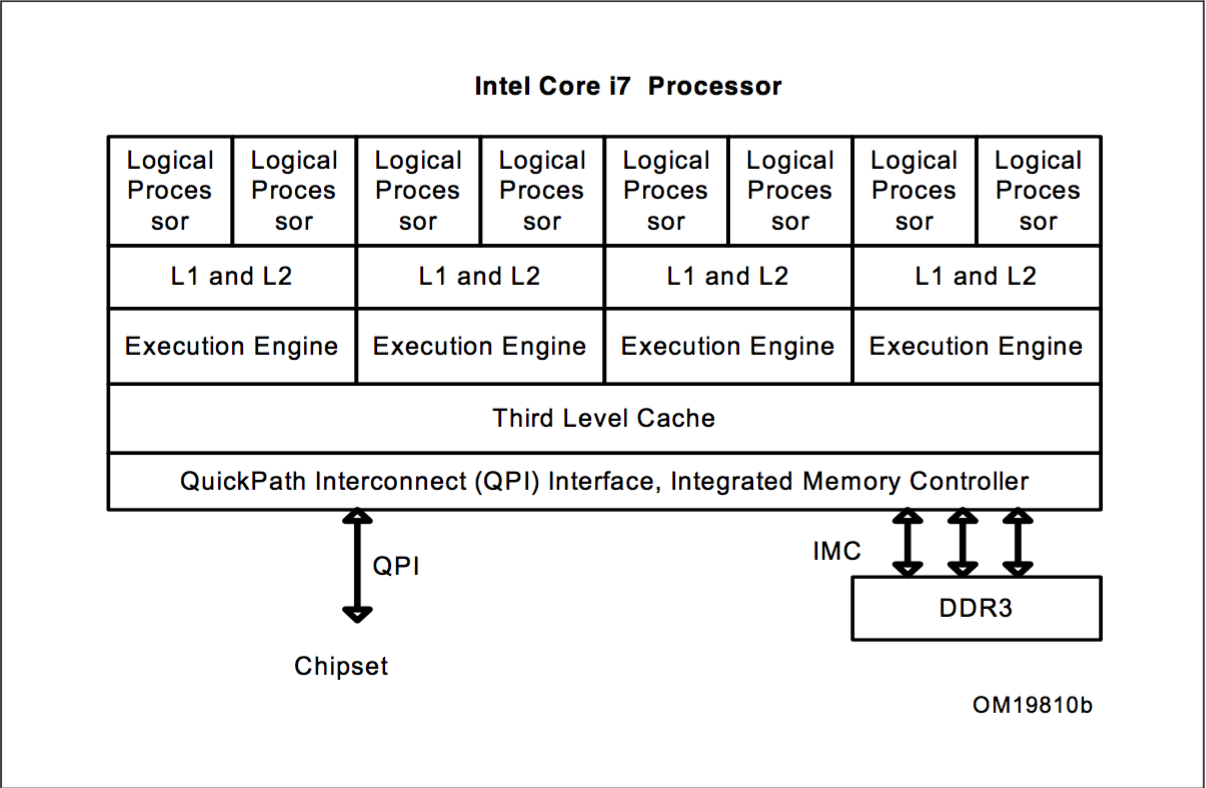

PCIe Literacy - PCIe Bus Basic Concept

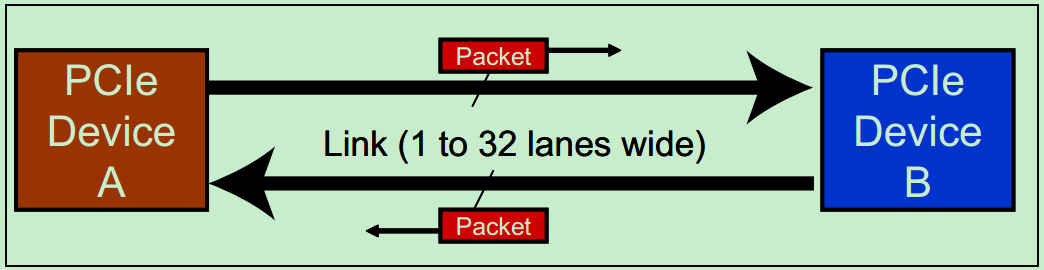

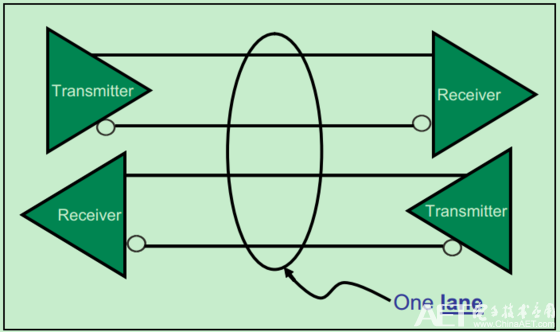

The PCIE bus can be regarded as the arrival of the traditional parallel bus to the development of the high-speed serial bus. In fact, not only the PCI bus to the PCIE bus, the high-speed serial bus re...

Basic concepts of PCIe bus

The introduction of the PCIe bus (Bus) represents the arrival of the development of the traditional parallel bus to a high-speed serial bus. However, in order to be compatible with PCI bus devices, al...

PCI/PCIe hardware related knowledge

Implementation of PCI Driver under Linux (Hardware) First of all, I would like to make a point. Since the author is not completely familiar with the kernel, I like to guess when doing kernel programmi...

PCIE knowledge point-003: upstream concept in PCIE protocol

1. The concept of protocol Upstream The protocol describes the concept of upstream as follows: 1)The relative position of an interconnect/System Element (Port/component) that is closer to the Root Com...

More Recommendation

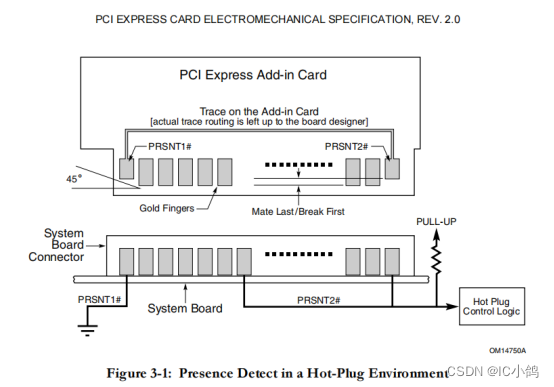

PCIE knowledge point-010: Where to get PCIE hot-swap information?

1. What information can be consulted about PCIE hot plugging? PCI Express Card Electromechanical Specification 2.0 PCI Express Base Specification Revision 5.0, Version 1.0 PCI Hot-Plug Specification R...

[PCI / PCIe bus] 1. Basic

PCI in the processor system The PCI bus stands for Peripheral Component Interconnect. It is part of the processor system and belongs to the local bus. Its main function is to connect external devices....

LTR: The practice of applying to knowledge base search in the field of e-commerce intelligent customer service

Keywords: search, machine learning, learning ranking, Learning to Rank (LTR) 1: background The optimization of search engine ranking (Ranking) is a common problem encounter...

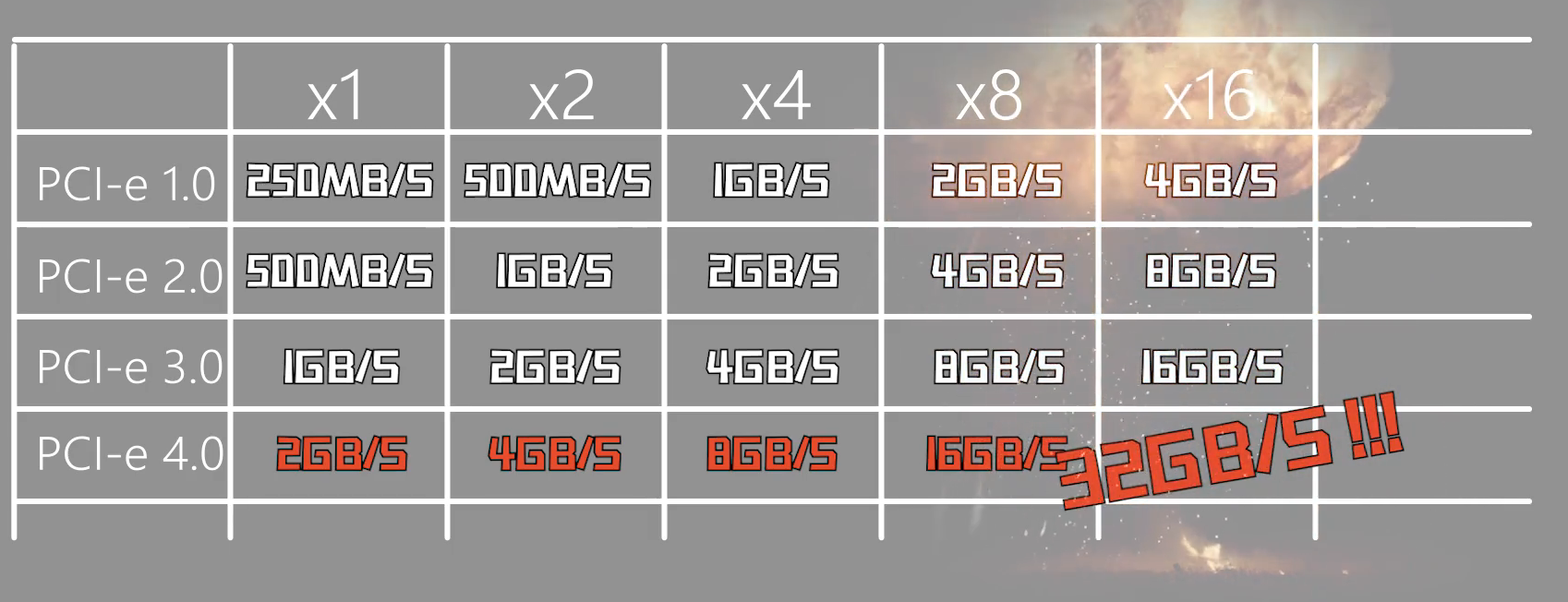

PCIe is

PCI-Express (Peripheral Component Interconnect Express) is a high-speed serial computer extension bus standard. Its original name is "3GIO", which is proposed by Intel in 2001 to replace the...

PCIe literacy - PCI bus basic concept

PCI is an abbreviation of Peripheral Component Interconnect (Peripheral Parts Interconnect), which once used the most widely used interface in your personal computer, almost all of the main board prod...