[VCS][UVM]UVM HDL Backdoor Access Setting

tags: Verifying engineers develop notes VCS SoC

UVM HDL Backdoor Access Setting

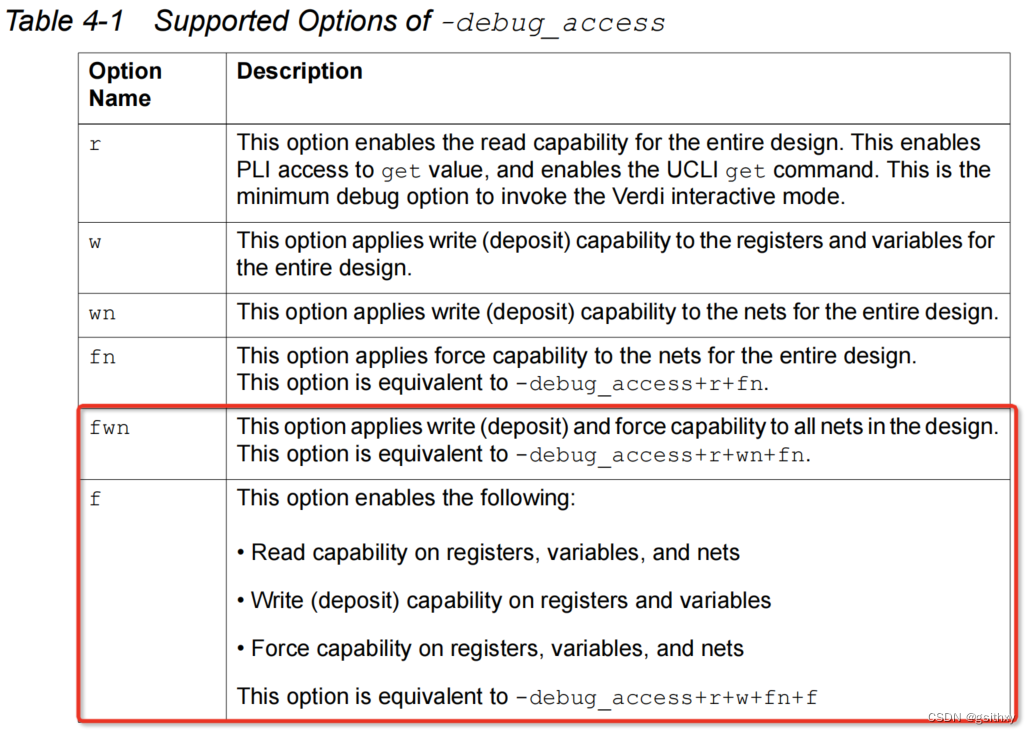

Foreword: In SOC verification, in order to improve the speed of compilation and simulation, we usually remove the option of debug_access+all. But doing this will cause a serious problem: UVM Backdoor Access will fail. So how can we guarantee both? This article will introduce a method.

1. Give Backdoor Access permissions to specify the specified Module through Module Name

First of all, you need to make a list to specify which module needs Backdoor access.

- soc_acc.tab

acc=frc,rw,wn:slave_dec

acc=frc,rw:bsc_reg_xaru- Come to eat this list in VCS compilation

-debug_access+pp -P ${PWA}/src/common/vcs/pli_table/soc_acc.tab- vcs option

Intelligent Recommendation

UVM: Register model access

content 1. Overwhelming 1.1. Write the actual value write set、update 1.2. Read the actual value read mirror、get 2. Back door access Establish a mapping 3. Forecast 4. Comparison and application Physic...

Teach you to build a basic UVM+VCS platform under Linux, run the first UVM code in "UVM Practical Battle" and output the results

Today, I am running the simplest verification platform in 2.2.1 in "UVM Practical Battle" to build a UVM verification platform with only drivers. The book only explains the code, but does no...

[Reprinted] [UVM] The most detailed introduction about the access method of uvm regmodel

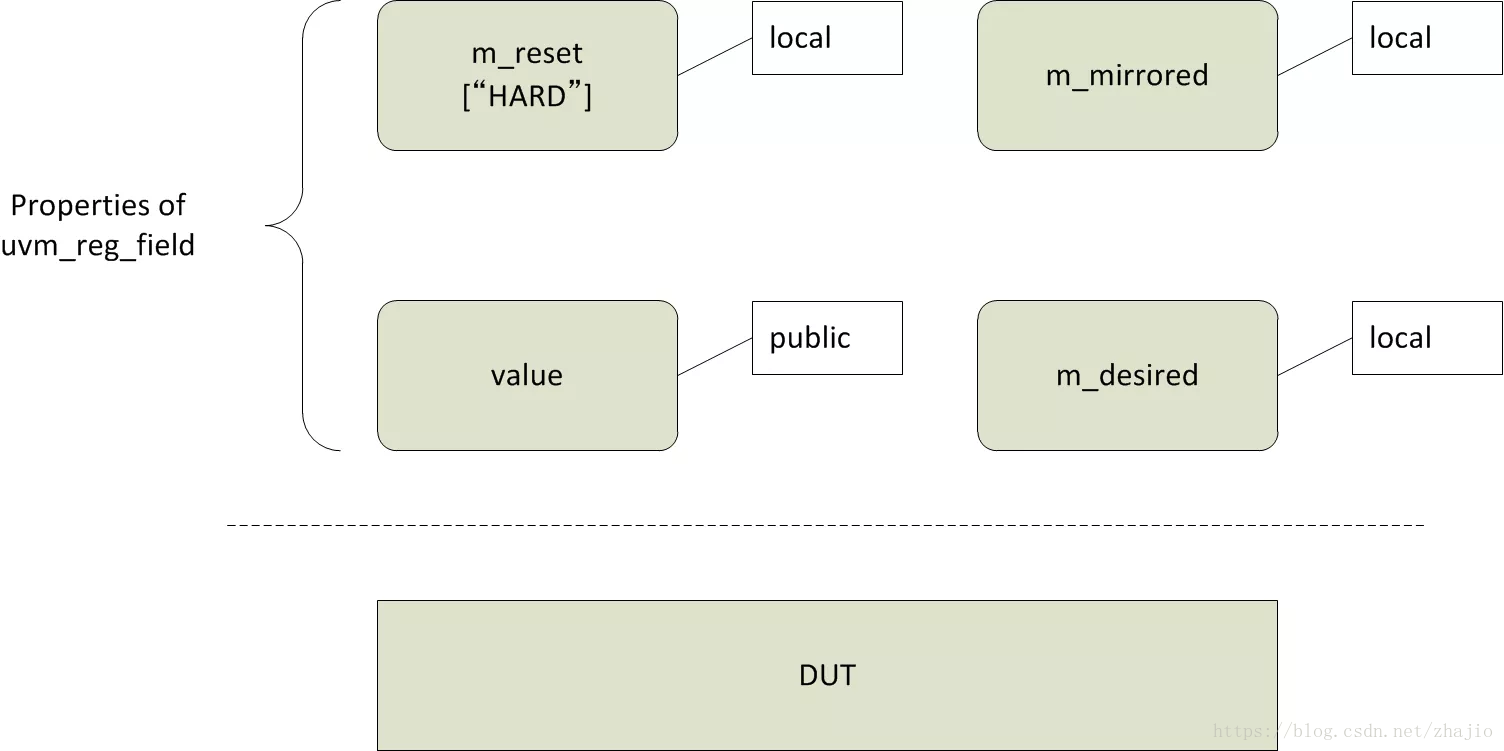

Note: This article is transferred fromUVM Tutorial for Candy Lovers – 16. Register Access Methods Translation fromUVM Candy Lovers Tutorial-16. Register Access Method The register ...

How to use the example of VCS and Verdi Rotation "UVM Battle"

Article catalog 1. Import the downloaded code into the virtual machine 2. Modification to files 3. Enter the VCS running code at the terminal Recently I plan to run the example of UVM actual combat to...

VCS, VERDI joint simulation, running "UVM actual combat"

VCS & VERDI joint simulation, running "UVM actual combat" After graduation, you will be a ICER (IC verification)! I have been studying myself in addition to graduation design recentlySV ...

More Recommendation

[VCS version] [Mentor's example] UVM -based UART verification environment

I accidentally saw someone shared in the group beforeMentor GraphicsThe UVM verification environment code provided by provided UART contains the basic use of UVM and the advanced UVM register model. S...

UVM learning road (2) — use VCS+VERDI for simulation debugging

UVM learning road (2) — use VCS+VERDI for simulation debugging I. Introduction Verdi was originally designed by Novas SoftWave. It belongs to SpringSoft. In the end, SpringSoft was acquired by S...

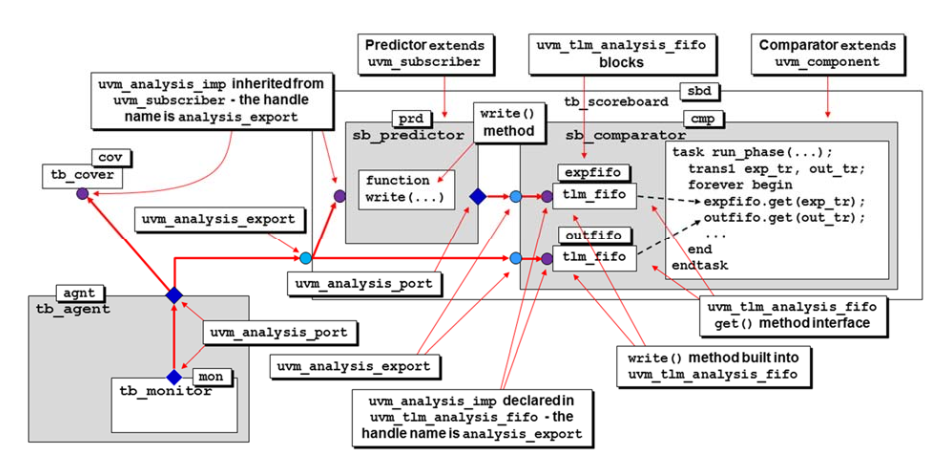

[UVM]Subscriber for UVM Component

First, Subscriber is used to receive Coverage, the following is a recommended way of writing: ...

[UVM]UVM Callback Example

Callback to corrupt the stimulus Let's consider an example of a Slave Driver (Slave Driver: drives response to the master). For simplicity, one callback hook is implemented and only response gene...

[UVM]UVM Port Fundamentals

UVM Port Fundamentals The UVM Base Class Library (BCL) includes base port classes t...