I accidentally saw someone shared in the group beforeMentor GraphicsThe UVM verification environment code provided by provided UART contains the basic use of UVM and the advanced UVM register model. Share it here.

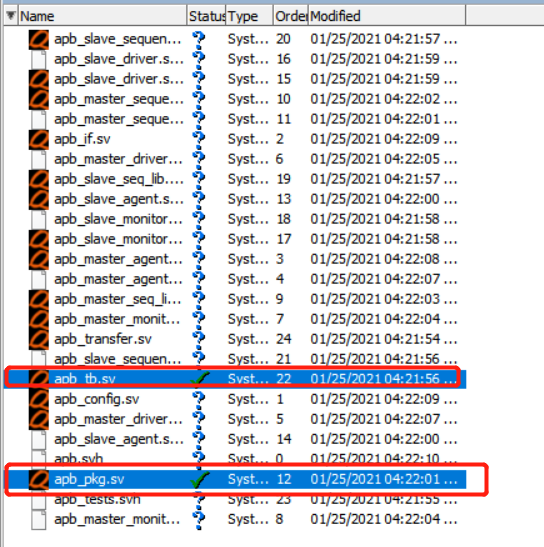

File description

agents/apb_agent - APB agent used in the UVM testbench

agents/uart_agent - UART agent user in the UVM testbench

agents/modem_agent - UART Modem interface agent, used in the UVM testbench

docs

protocol_monitor - contains an example APB protocol monitor

rtl - Contains the UART RTL source code***

sim - Simulation directory for the example, contains the Makefile

uvm_tb/tb - Top level testbench

uvm_tb/tests

uvm_tb/virtual_sequences

uvm_tb/sequences

uvm_tb/register_model

uvm_tb/env - contains the functional coverage monitors described in the cookbookDUT is a 16550A UART module. The interface mainly contains APB, UART, and some status signals. Agents are agent of different interfaces. 16550A UART recommends that you can search and download detailed SPEC.

DOCS is a simple description of the UART module, which contains some instructions for some registers

Protocol_monitor is an protocol check module.

Environmental integration and Sequence are written under UVM_TB.

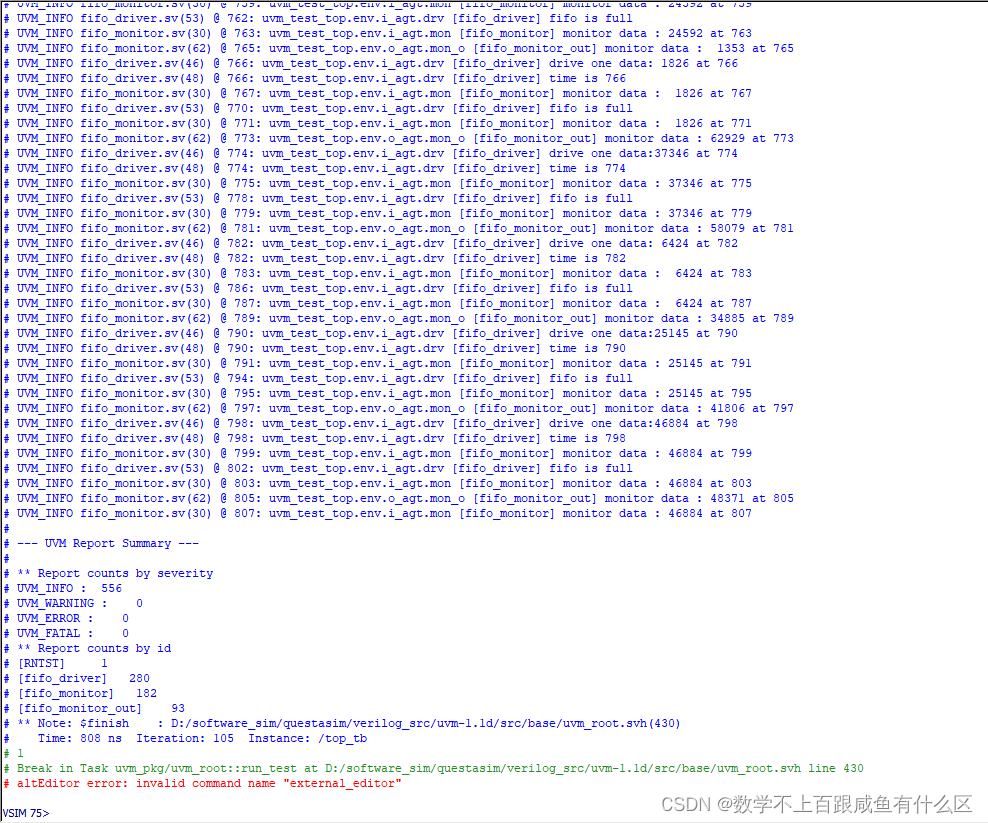

Run simulation

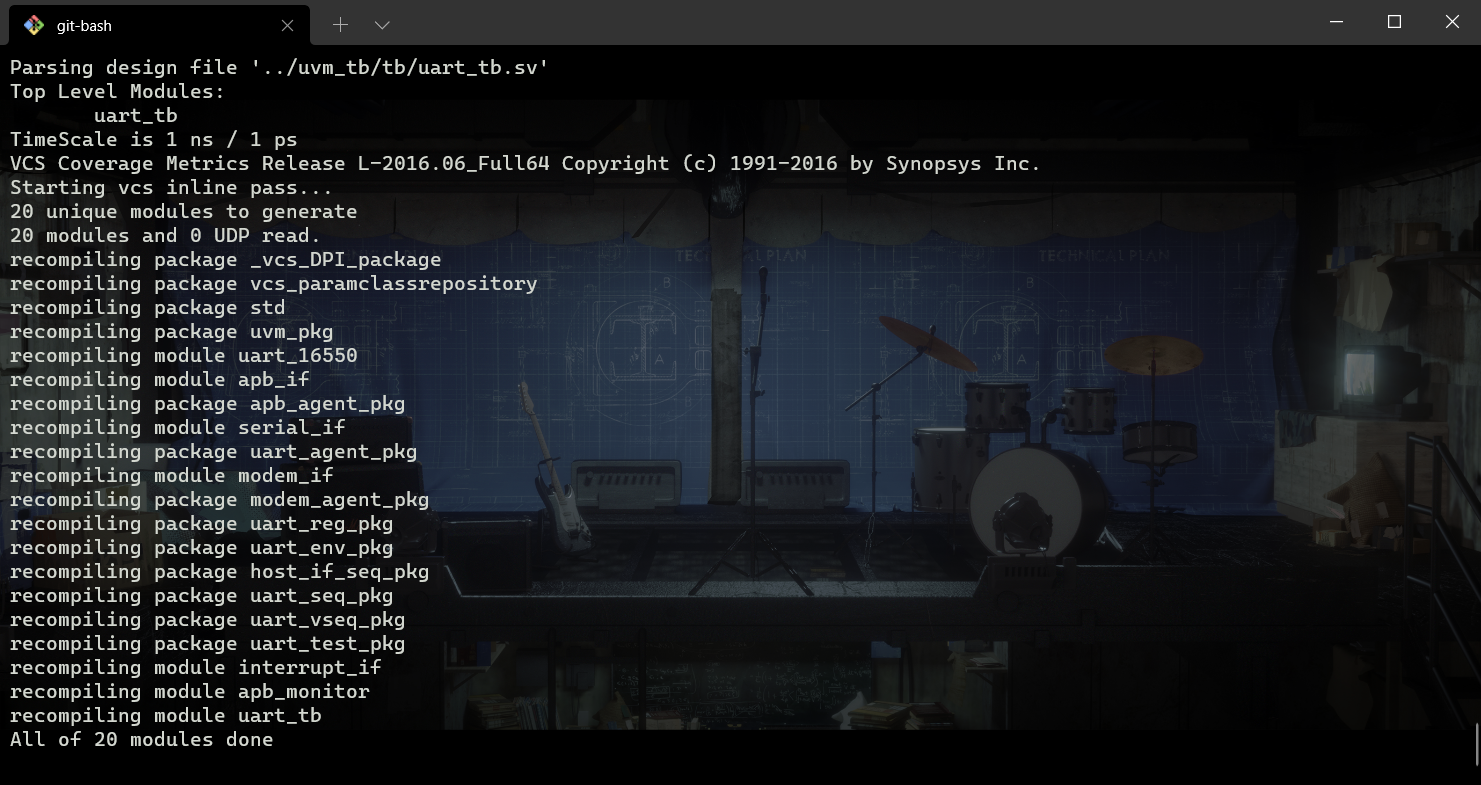

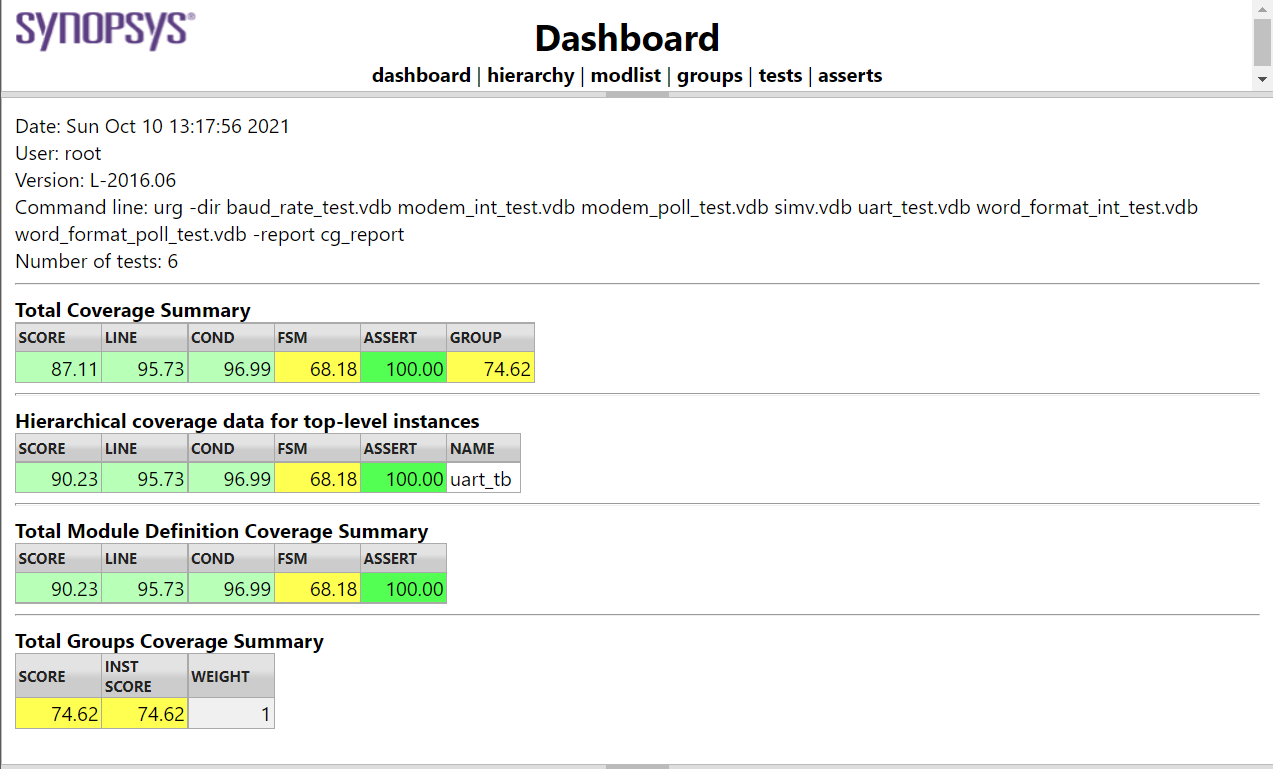

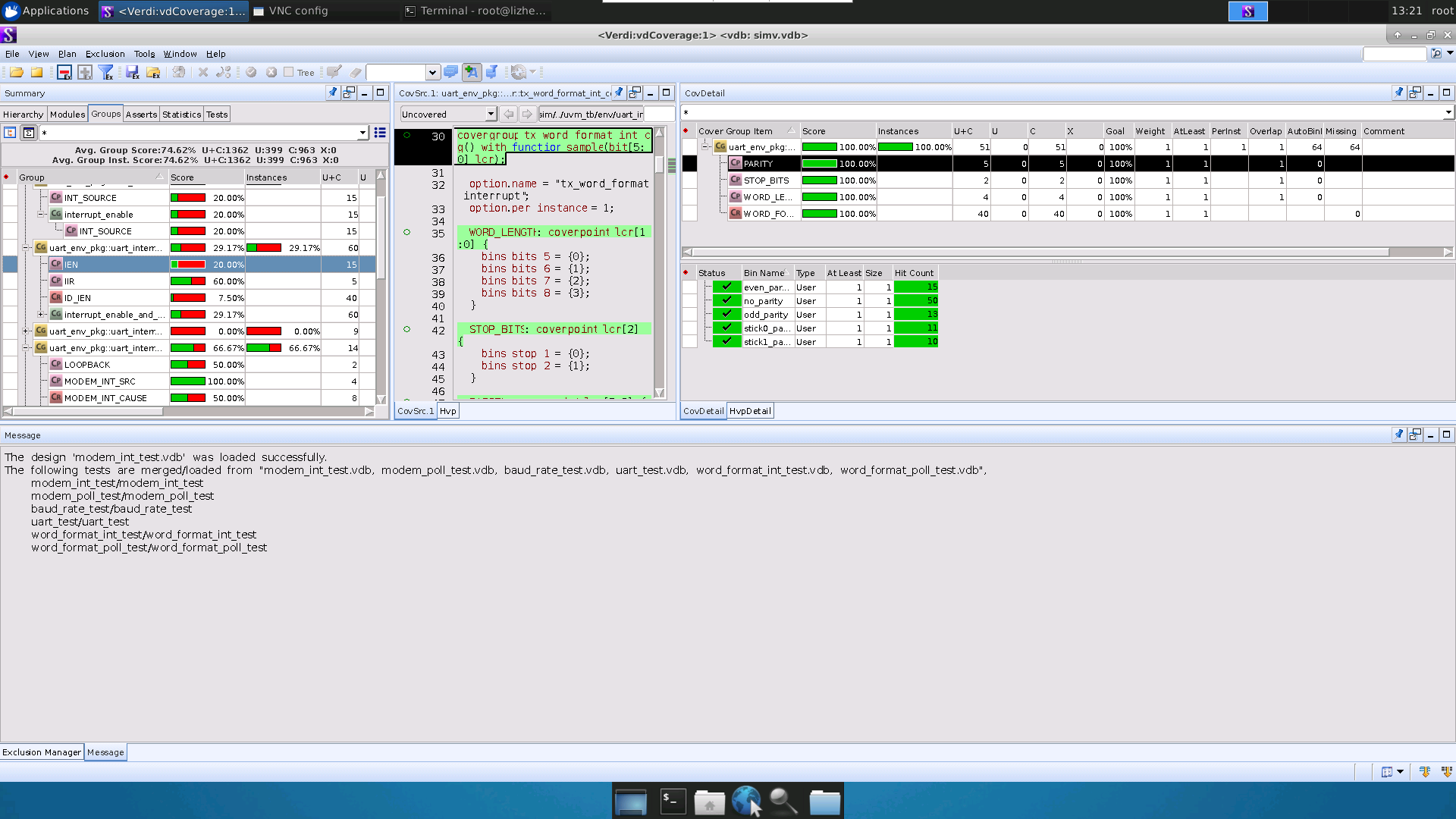

Because it is an example provided by MENTOR, the original Makefile calls Questa. This time I changed the Makefile, run with VCS, and then generate the web report after generating coverage, or use Verdi to view the coverage.

Make all run

The coverage report is generated in the cg_report directory

Make Verdi_cg use Verdi to view coverage

The testcase written in the example does not reach 100%coverage. If you are interested, you can try to write a new Case yourself to improve the coverage

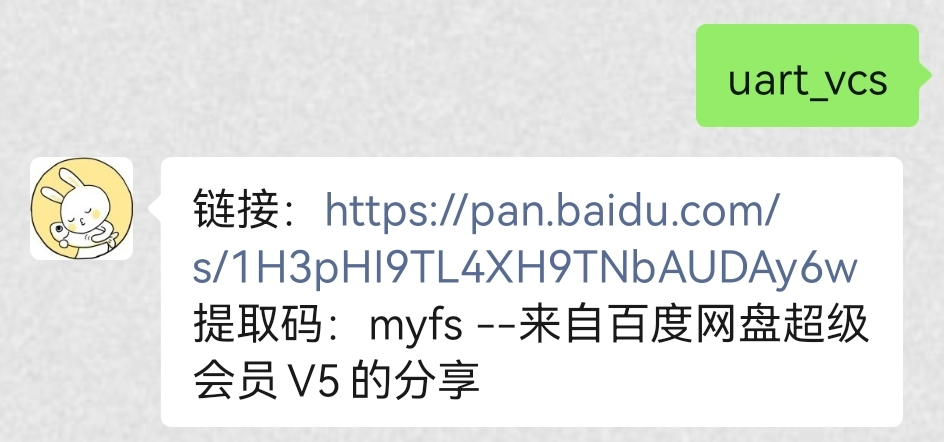

Background reply

uart_vcsGet the verification environment

In addition, the simulation EDA tool can also read the following article