Verilog HDL (6): State machine detects 11101 sequence

tags: Verilog HDL

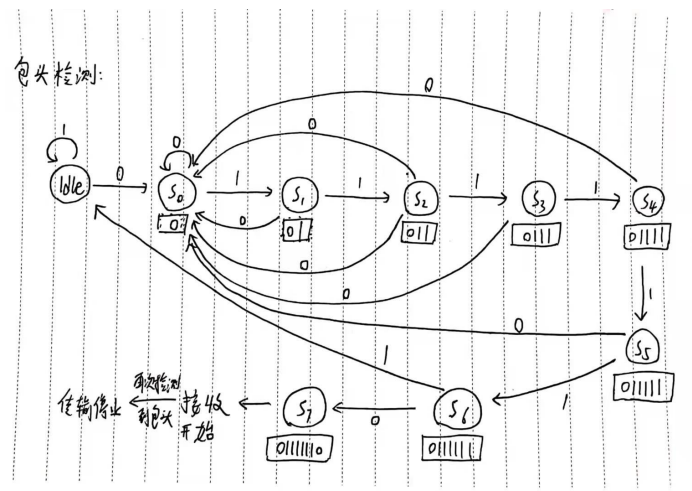

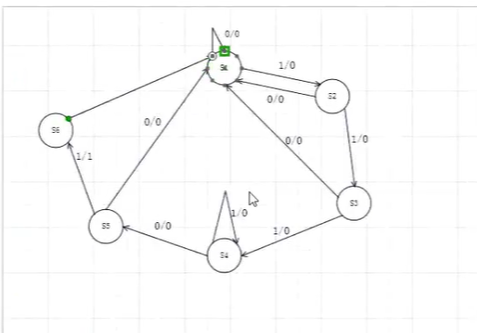

Detect the 11101 sequence and draw a state transition diagram.

1. State transition diagram (Mealy type) Input/Output

2. Code

Create fsm11101 file

//Two-stage

module fsm11101(

input wire sclk,

input wire rst_n,

input wire A,

output reg k

);

parameter s1=6'b000001;

parameter s2=6'b000010;

parameter s3=6'b000100;

parameter s4=6'b001000;

parameter s5=6'b010000;

parameter s6=6'b100000;

reg [5:0] state;

always @(posedge sclk or negedge rst_n)

if(rst_n==1'b0)

state<=s1;

else

case(state)

s1:

if(A==1'b1)

state<=s2;

else

state<=s1;

s2:

if(A==1'b1)

state<=s3;

else

state<=s1;

s3:

if(A==1'b1)

state<=s4;

else

state<=s1;

s4:

if(A==1'b1)

state<=s4;

else

state<=s5;

s5:

if(A==1'b1)

state<=s6;

else

state<=s1;

s6:state<=s1;

default:state<=s1;

endcase

always @(posedge sclk or negedge rst_n)

if(rst_n==1'b0)

k<=1'b0;

else if(state==s5 && A==1'b1)

k<=1'b1;

else

k<=1'b0;

endmodule 3.testbeach

Create tb_fsm11101 file

`timescale 1ns/1ns

module tb_fsm11101;

reg sclk,rst_n;

reg a_in;

wire k_out;

initial begin

sclk=0;

rst_n=0;

#100;

rst_n=1;

end

initial begin

#200;

rand_bit();

end

always #10 sclk<=~sclk;

fsm11101 fsm11101_inst(

.sclk (sclk),

.rst_n (rst_n),

.A (a_in),

.k (k_out)

);

task rand_bit();

integer i;

begin

for(i=0;i<255;i=i+1)

begin

@(posedge sclk);

a_in<={$random} %2; //Generate 0--1

end

end

endtask

endmodule

4. Simulation (ModelsimSE-64 simulation)

Build simulation script run.do file (use script file to write more convenient)

quit -sim

.main clear

#

vlib ./lib/

vlib ./lib/work_a/

vlib ./lib/design/

#MAP Map base_space to ./lib/work_a/ base_space and design are two logic libraries

vmap base_space ./lib/work_a/

vmap design ./lib/design/

#Compile-work Compile tb_fsm11101.v in this folder into the base_space logic library

vlog -work base_space ./tb_fsm11101.v

#.. is to turn up a folder, see the design folder, compile all the .v files in this folder to the logic library of design

vlog -work design ./../design/*.v

#start up

#-t The accuracy of the event to run the simulation is ns

#-L is a keyword for linking libraries

vsim -t ns -voptargs=+acc -L base_space -L design base_space.tb_fsm11101

#Add virtual structure

virtual type {

{01 s1}

{02 s2}

{04 s3}

{08 s4}

{10 s5}

{20 s6}

} vir_new_signal

#add wave -divider{tb_sim}

add wave tb_fsm11101/*

#add wave -divider{des}

#Top level + instantiated name/* where * is a wildcard, matching all signals

add wave tb_fsm11101/fsm11101_inst/*

#Create (vir_new_signal) type signal, convert state signal to new_state signal

virtual function {(vir_new_signal)tb_fsm11101/fsm11101_inst/state} new_state

add wave -color red tb_fsm11101/fsm11101_inst/new_state

run 1us

Notes:

These three statements are to convert the state signal into a new_state signal. You can clearly see s1, s2...s6 in the figure below

#Add virtual structure

virtual type {

{01 s1}

{02 s2}

{04 s3}

{08 s4}

{10 s5}

{20 s6}

} vir_new_signal#Create (vir_new_signal) type signal, convert state signal to new_state signal

virtual function {(vir_new_signal)tb_fsm11101/fsm11101_inst/state} new_stateadd wave -color red tb_fsm11101/fsm11101_inst/new_state

5. Results

Intelligent Recommendation

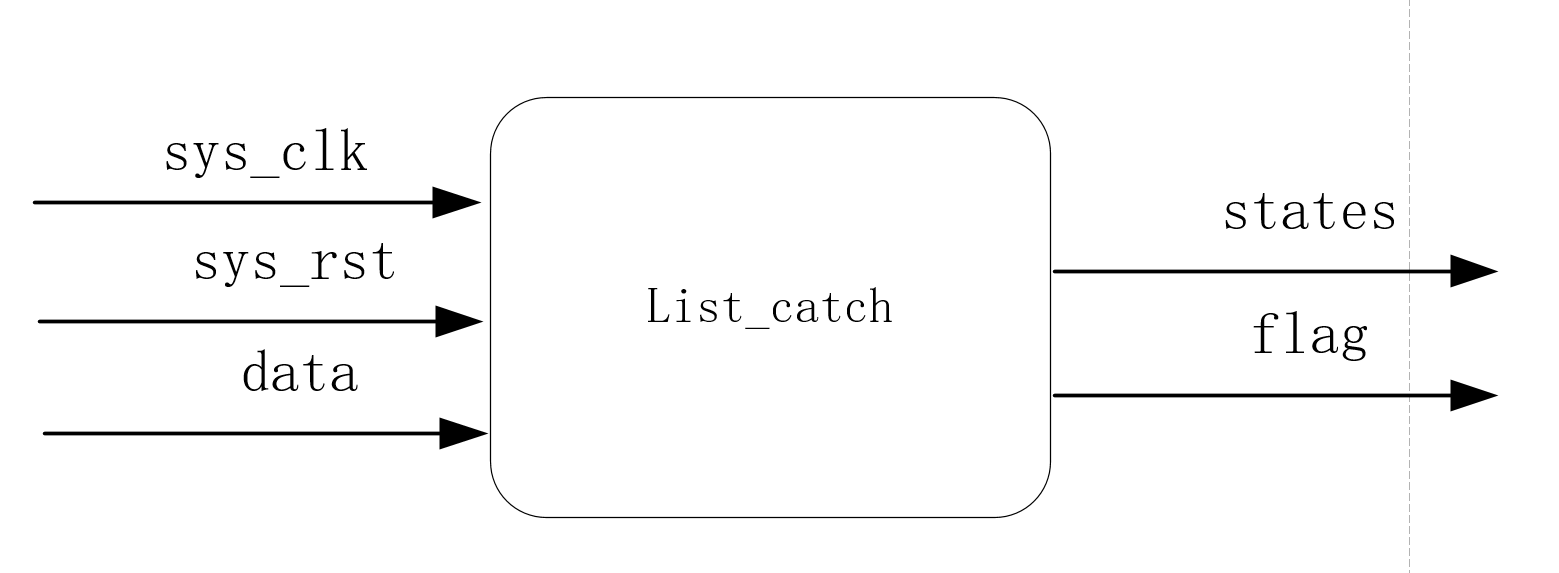

Verilog state machine implementation sequence capture circuit

State machine implementation sequence capture circuit Title requirements Design a six-bit sequence capture circuit with a state machine: The input sequence is 0x5c7b1de, the sequence capture 0x36, and...

Sequence detection: state machine and shift register (Verilog)

RTL code: Simulation code: ** Simulation: ** Note the difference between the two simulation results...

Verilog Sequence Detector State Machine Register Writing

State machine writing Ability to detect overlapping portions Register writing: the difference The shift register needs to store all codewords, so if the sequence length is n, the method needs to consu...

Verilog code writing state machine - sequence detection

topic: There is a special serial communication system, and the data is transmitted in the form of a package, and the data of the data is 01111110 , Then for the data content, then01111110 End, now you...

[Verilog HDL] 6. Ten frequency

[@TOC] [1. Source code] [2. Simulation]...

More Recommendation

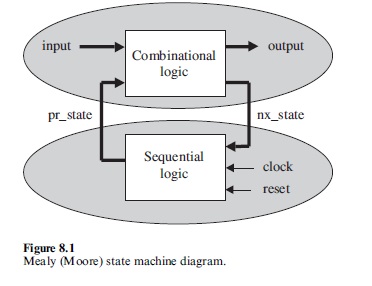

Verilog HDL implements the status machine

1. Introduction to status machine The state machine is abbreviated as FSM (Finite State Machine), also known as synchronous limited state machine. Category: Moore -type state machine, output is relate...

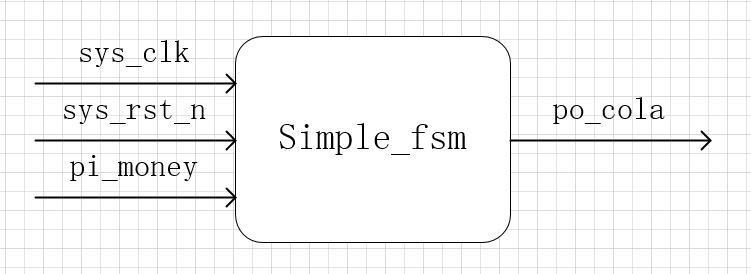

FPGA verilog HDL based on finite state machine design vending machine and synthesis

Project: FPGA verilog HDL based on finite state machine design vending machine and synthesis Application module:Button anti-shake module, finite state machine module, LED module (breathing lamp, two-w...

HDL / FPGA learning note seven: Sequence detector Moore state machine and mealy state machine implementation

First, Moore State Machine Design a sequence detector, detect sequence 1101, detect output 1, otherwise output 0. Second, MEALY state machine Design a sequence detector. When the detector is required ...

Verilog topic (31) Sequence Recognition (sequence recognition state machine)

HDLBits URL: https://hdlbits.01xz.net/wiki/Main_Page topic Data frame sending involves decoding consecutive bits of data (bit-stream) to look for bit flags (flag) that indicate the beginning an...

Finite state machine HDL template

Logical design, as the name suggests, as long as it is clearLogicwith TimingThe rest of the design is just a fill-in-the-blank question. The standard design of the finite state machine is given below,...