[UVM]UVM Port Fundamentals

tags: UVM

UVM Port Fundamentals

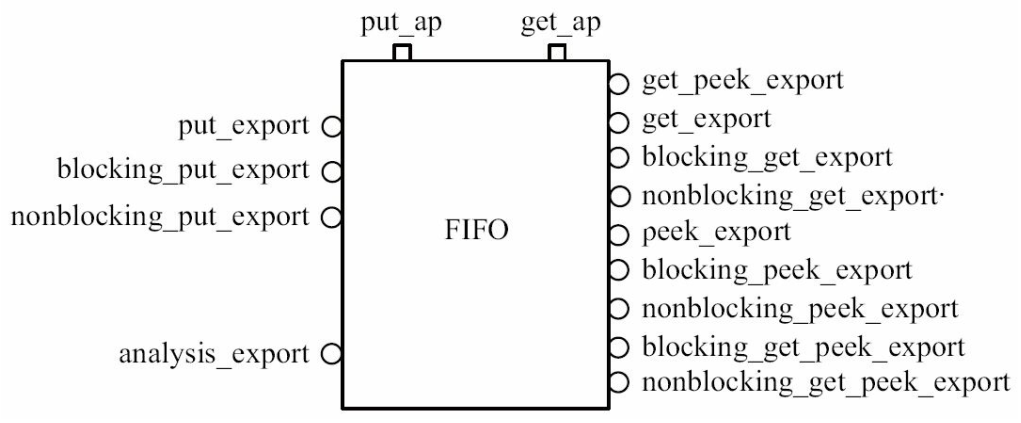

The UVM Base Class Library (BCL) includes base port classes that are extended to define the TLM1(Transaction Level Model 1) ports that are used in UVM verification environments.

A, UVM port connection chains

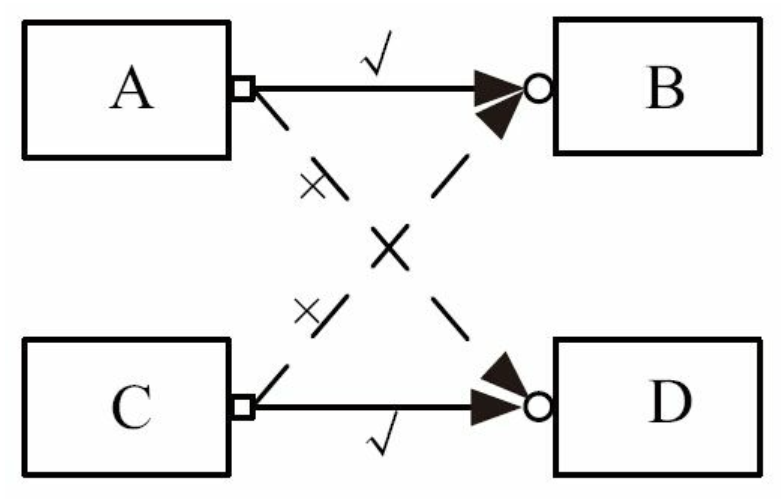

- UVM TLM connections include chains of port(s) – (exports(s)(optional)) – imp(s)(implementations

1.1、UVM Ports

- UVM ports initiate transaction activity and can connect to: (1) other UVM ports, (2) UVM exports, and (3) UVM imps.

1.2、UVM Exports

- UVM exports are basically transfer‐ports that can connect to: (1) other UVM exports, and (2) UVM imps.

1.3、UVM Imps

- UVM imps (implementations) terminate a chain of port(s)‐(export(s))‐imp.

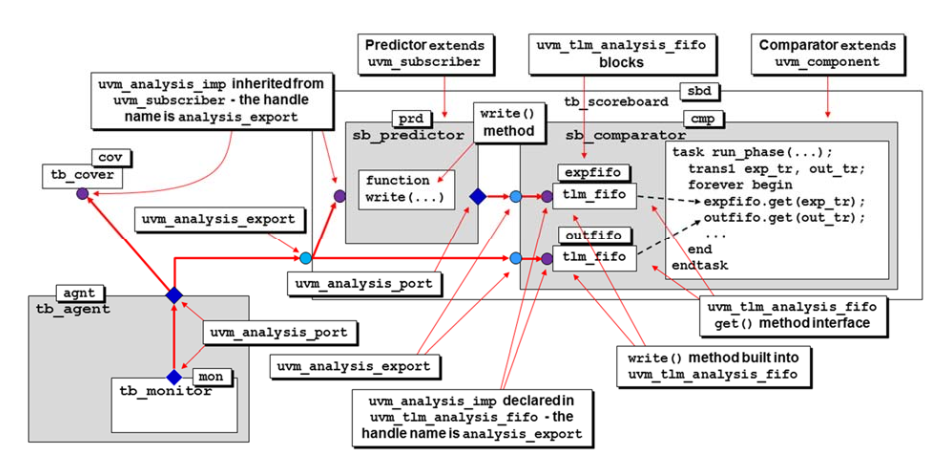

1.4、Unfortunate port naming convention

- An unfortunate naming convention inside of UVM makes the imp‐connections rather confusing. UVM documentation teaches about ports connecting to exports and is somewhat vague about imps. In fact the uvm_sequencer base class includes a seq_item_export handle declaration, but this so‐called "export" handle is really a uvm_seq_item_pull_imp port type. Similarly, the uvm_subscriber base class, which is frequently extended to help create scoreboards and coverage collectors, has an analysis_export handle declaration, but this so‐called "export" handle is really a uvm_analysis_imp port type.

1.5、Port‐Export‐Imp chains

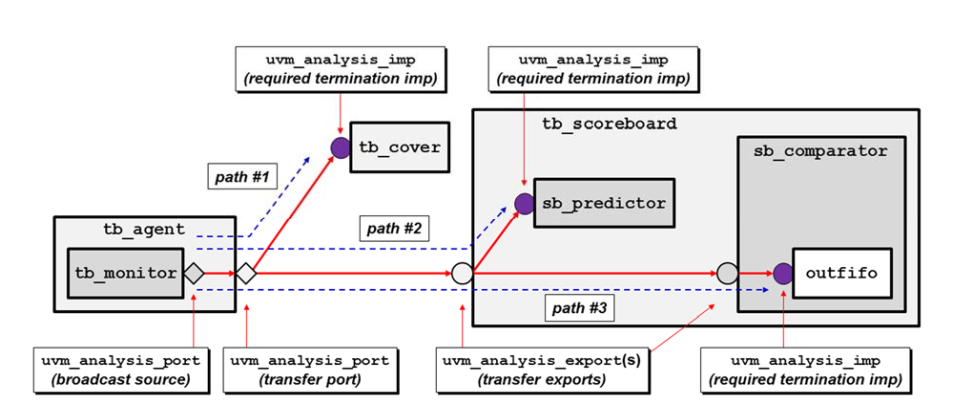

- Most port‐export‐imp chains only allow a single connection point. The driver‐sequencer is a common example in UVM where the driver port ( seq_item_port ) connects to the sequencer export ( seq_item_export – which is really an implementation port).The broadcast port type in UVM is the uvm_analysis_port. This port type is allowed to connect to multiple port‐export‐imp chains, each of which must terminate with a uvm_analysis_imp. Figure 3 (on page15) shows two common analysis paths that are used in a UVM testbench.The common sets of paths are shown in Figure 4. The first analysis paths originate with a uvm_analysis_port on the tb_monitor that broadcasts to another uvm_analysis_port on the tb_agent, which then branches into two paths with the first path (labeled Path #1) terminating at the uvm_analysis_imp on the tb_cover coverage collector. The second branch from the tb_agent connects to the uvm_analysis_export on the tb_scoreboard. The uvm_analysis_export on the tb_scoreboard then branches into two paths with the first path (labeled path #2) terminating at a uvm_analysis_imp port on the sb_predictor (extended from the uvm_subscriber), and the second path (labeled path #3) connects to a uvm_analysis_export on the sb_comparator, which then terminates at a uvm_analysis_imp on the uvm_tlm_analysis_fifo with handle name outfifo.

Intelligent Recommendation

[UVM]UVM RAL Adapter

UVM RAL Adapter With the UVM Register mo...

[UVM]UVM TLM Export

UVM TLM Export The TLM Export is a port that forwards a transaction from a...

UVM ——UVM (sequence)

content 、sequence 5.1sequence 5.2sequence ——start()/default_sequence 5.3sequence ——body() `uvm_do(): 5.4sequence 5.4.1 5.4.2 、sequence UVM sequence test case testbench 。 ,testb...

[The UVM] be verified by APB_RD PORT APB_WR with RAL Test

In the process of verification of the register, and also to verify whether the BUS can pass, whether APB PORT are right. For example, sometimes give Modul stay two or more sets of APB interface, and s...

(4) Port and debugging on the FIFO of UVM TLM Communication

Port and debugging on the FIFO of TLM Communication Port and commissioning on FIFO FiFo and IMP Port and commissioning on FIFO Although all the names represented in the above figure Although exports a...

More Recommendation

(4) Interconnection of the port of UVM TLM communication

UVM TLM communication port interconnection Connection between port and export Connection between Port and Import Connection between export and IMP Connection between Port and PORT Connection between E...

[UVM] Do not use Factory Create Port

The ITEM type passed between PORT must be consistent, and the item of the parent-sub-class relationship is not working....

[UVM] UVM Barrier for UVM process synchronization (2)

UVM Barrier One, uvm_barrier in function ...

[UVM] UVM Barrier for UVM process synchronization (1)

UVM Barrier The uvm barrier class ...

[UVM] uvm event callback for UVM process synchronization

uvm event callback UVM provides the facil...